- 數位電子教程

- 數位電子 - 首頁

- 數位電子基礎

- 數字系統型別

- 訊號型別

- 邏輯電平和脈衝波形

- 數字系統元件

- 數字邏輯運算

- 數字系統優勢

- 數制

- 數制

- 二進位制數表示

- 二進位制運算

- 有符號二進位制運算

- 八進位制運算

- 十六進位制運算

- 補碼運算

- 進位制轉換

- 進位制轉換

- 二進位制到十進位制轉換

- 十進位制到二進位制轉換

- 二進位制到八進位制轉換

- 八進位制到二進位制轉換

- 八進位制到十進位制轉換

- 十進位制到八進位制轉換

- 十六進位制到二進位制轉換

- 二進位制到十六進位制轉換

- 十六進位制到十進位制轉換

- 十進位制到十六進位制轉換

- 八進位制到十六進位制轉換

- 十六進位制到八進位制轉換

- 二進位制編碼

- 二進位制編碼

- 8421 BCD碼

- 餘3碼

- 格雷碼

- ASCII碼

- EBCDIC碼

- 程式碼轉換

- 錯誤檢測與糾錯碼

- 邏輯閘

- 邏輯閘

- 與門

- 或門

- 非門

- 通用門

- 異或門

- 異或非門

- CMOS邏輯閘

- 使用二極體電阻邏輯的或門

- 與門與或門

- 兩級邏輯實現

- 閾值邏輯

- 布林代數

- 布林代數

- 布林代數定律

- 布林函式

- 德摩根定理

- SOP和POS形式

- POS到標準POS形式

- 最小化技術

- 卡諾圖最小化

- 三變數卡諾圖

- 四變數卡諾圖

- 五變數卡諾圖

- 六變數卡諾圖

- 無關項

- 奎因-麥克斯拉斯基法

- 最小項和最大項

- 規範式和標準式

- 最大項表示

- 使用布林代數簡化

- 組合邏輯電路

- 數字組合電路

- 數字算術電路

- 多路複用器

- 多路複用器設計流程

- MUX通用門

- 使用4:1 MUX的2變數函式

- 使用8:1 MUX的3變數函式

- 多路分解器

- MUX與DEMUX

- 奇偶校驗位生成器和校驗器

- 比較器

- 編碼器

- 鍵盤編碼器

- 優先編碼器

- 譯碼器

- 算術邏輯單元

- 7段LED顯示器

- 程式碼轉換器

- 程式碼轉換器

- 二進位制到十進位制轉換器

- 十進位制到BCD轉換器

- BCD到十進位制轉換器

- 二進位制到格雷碼轉換器

- 格雷碼到二進位制轉換器

- BCD到餘3碼轉換器

- 餘3碼到BCD轉換器

- 加法器

- 半加器

- 全加器

- 序列加法器

- 並行加法器

- 使用半加器的全加器

- 半加器與全加器

- 使用與非門的全加器

- 使用與非門的半加器

- 二進位制加法/減法器

- 減法器

- 半減器

- 全減器

- 並行減法器

- 使用2個半減器的全減器

- 使用與非門的半減器

- 時序邏輯電路

- 數字時序電路

- 時鐘訊號和觸發

- 鎖存器

- 移位暫存器

- 移位暫存器應用

- 二進位制暫存器

- 雙向移位暫存器

- 計數器

- 二進位制計數器

- 非二進位制計數器

- 同步計數器設計

- 同步計數器與非同步計數器

- 有限狀態機

- 演算法狀態機

- 觸發器

- 觸發器

- 觸發器轉換

- D觸發器

- JK觸發器

- T觸發器

- SR觸發器

- 帶時鐘的SR觸發器

- 無時鐘的SR觸發器

- 帶時鐘的JK觸發器

- JK到T觸發器

- SR到JK觸發器

- 觸發方式:觸發器

- 邊沿觸發觸發器

- 主從JK觸發器

- 競爭冒險現象

- A/D和D/A轉換器

- 模數轉換器

- 數模轉換器

- DAC和ADC積體電路

- 邏輯閘的實現

- 用與非門實現非門

- 用與非門實現或門

- 用與非門實現與門

- 用與非門實現或非門

- 用與非門實現異或門

- 用與非門實現異或非門

- 用或非門實現非門

- 用或非門實現或門

- 用或非門實現與門

- 用或非門實現與非門

- 用或非門實現異或門

- 用或非門實現異或非門

- 使用CMOS的與非/或非門

- 使用與非門的全減器

- 使用2:1 MUX的與門

- 使用2:1 MUX的或門

- 使用2:1 MUX的非門

- 儲存器件

- 儲存器件

- RAM和ROM

- 快取記憶體儲存器設計

- 可程式設計邏輯器件

- 可程式設計邏輯器件

- 可程式設計邏輯陣列

- 可程式設計陣列邏輯

- 現場可程式設計門陣列

- 數字電子系列

- 數字電子系列

- CPU架構

- CPU架構

- 數位電子資源

- 數位電子 - 快速指南

- 數位電子 - 資源

- 數位電子 - 討論

可程式設計邏輯器件

可程式設計邏輯器件 (PLD) 是一組積體電路,可以配置為執行各種邏輯功能。PLD 在工程和技術領域發揮著重要作用,因為它們構成了創新的基礎,並支援工程師開發自動化數字系統以提高流程的靈活性和效率。這裡,“可程式設計”意味著定義一個可以多次執行而無需人工干預的功能。

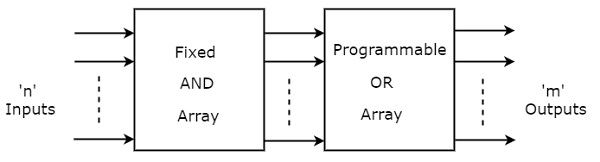

可程式設計邏輯器件(PLD) 是積體電路。它們包含一個與門陣列和另一個或門陣列。根據具有可程式設計功能的陣列型別,有三種類型的 PLD。

- 可程式設計只讀儲存器

- 可程式設計陣列邏輯

- 可程式設計邏輯陣列

將資訊輸入這些裝置的過程稱為程式設計。基本上,使用者可以對這些器件或積體電路進行電氣程式設計,以根據需要實現布林函式。這裡,術語“程式設計”指的是硬體程式設計,而不是軟體程式設計。

在本章中,我們將解釋可程式設計邏輯器件的基本概念、型別、優點、侷限性和應用。

可程式設計只讀儲存器 (PROM)

只讀儲存器 (ROM) 是一種儲存器裝置,它永久地儲存二進位制資訊。這意味著,我們以後無法透過任何方式更改儲存的資訊。如果ROM具有可程式設計功能,則稱為可程式設計ROM (PROM)。使用者可以使用PROM程式設計器一次電氣程式設計二進位制資訊。

PROM是一種可程式設計邏輯器件,具有固定與陣列和可程式設計或陣列。PROM的框圖如下所示。

這裡,與門的輸入不是可程式設計型別。因此,我們必須使用2n個具有n個輸入的與門來生成2n個積項。我們可以使用nx2n譯碼器實現這些積項。因此,此譯碼器生成“n”個最小項。

這裡,或門的輸入是可程式設計的。這意味著,我們可以程式設計任何數量所需的積項,因為所有與門的輸出都作為輸入應用於每個或門。因此,PROM的輸出將以最小項之和的形式出現。

示例

讓我們使用PROM實現以下布林函式。

$$\mathrm{A(X,Y,Z)\:=\:\sum m\left ( 5,6,7 \right )}$$

$$\mathrm{B(X,Y,Z)\:=\:\sum m\left ( 3,5,6,7 \right )}$$

給定的兩個函式以最小項之和的形式給出,每個函式都有三個變數X、Y和Z。因此,我們需要一個3到8譯碼器和兩個可程式設計或門來產生這兩個函式。相應的PROM如下所示。

這裡,3到8譯碼器生成八個最小項。兩個可程式設計或門可以訪問所有這些最小項。但是,為了透過每個或門產生相應的布林函式,僅對所需的最小項進行程式設計。符號“X”用於可程式設計連線。

什麼是可程式設計邏輯器件?

可程式設計邏輯器件 (PLD) 可以定義為可以程式設計以執行特定功能的積體電路 (IC)。這裡,程式設計意味著我們可以定義一組可以執行以多次執行功能的指令,而無需任何人工干預。

開發PLD的主要需求是實現可以複製傳統邏輯電路行為並多次複製它的數字邏輯功能。但是,PLD在可程式設計性方面不同於普通的數字邏輯電路,這意味著我們可以透過在器件中設定一組指令來定義所需的邏輯功能。

PLD型別

根據所用器件的型別,可程式設計邏輯器件 (PLD) 可以分為以下兩種型別:

- 雙極型PLD

- CMOS PLD

讓我們詳細討論每種型別的可程式設計邏輯器件。

雙極型PLD

雙極型PLD是可程式設計邏輯器件的型別,其中雙極結型電晶體 (BJT) 是主要的功能器件。雙極型PLD是可程式設計邏輯器件的早期版本。因此,在開發CMOS PLD之前,它們被廣泛使用。

以下是雙極型可程式設計邏輯器件的一些重要特性:

- 雙極型PLD提供快速的開關速度,因此它們可以在更高的頻率下工作。

- 雙極型PLD更適合涉及快速訊號處理並需要快速響應時間的應用。

- 雙極型PLD需要更多的功率來執行。

- 雙極型PLD對電子噪聲和干擾具有更好的免疫力。

所有這些特性使雙極型可程式設計邏輯器件非常適合用於高速執行和可靠性至關重要的應用,例如航空航天、軍事和電信系統。

CMOS PLD

CMOS PLD代表互補金氧半導體可程式設計邏輯器件。顧名思義,CMOS PLD使用CMOS電晶體,即NMOS(N溝道金氧半導體)和PMOS(P溝道金氧半導體)電晶體作為基本元件。

CMOS PLD基本上是PLD的現代版本,由於其眾多優點,在現代數字系統中得到廣泛使用。

下面描述了CMOS PLD的一些重要特性:

- CMOS PLD執行所需的功率非常少。因此,此特性使CMOS PLD非常適合用於電池供電裝置,在這些裝置中,能源效率是一個重要因素。

- CMOS PLD更可靠且更健壯。因為它們設計用於承受各種環境因素,例如高溫/低溫、電壓波動和不同的輻射干擾。

- CMOS PLD在可擴充套件性方面也很出色。

CMOS PLD是更新的PLD器件,因此在各種現代電子裝置中非常常用,例如消費電子產品、醫療裝置、工業自動化系統、汽車系統。

PLD程式語言

在可程式設計邏輯器件(PLD)的情況下,使用多種不同的硬體描述語言(HDL)對其進行程式設計。使用這些PLD程式語言,工程師和設計師可以定義PLD電路的行為和邏輯功能。

這裡描述了一些最常用的PLD程式語言:

VHDL

VHDL代表VHSIC硬體描述語言。它是一種標準化的硬體描述語言,用於對數位電路和系統進行建模和模擬。使用VHDL,工程師和開發人員可以指定數位電路的結構和功能。VHDL非常適合組合電路和時序電路,因為它支援併發和順序描述。

VHDL是設計和驗證高度複雜的數位電路和系統(如PLD、ASIC、FPGA等)最廣泛使用的程式語言之一。

Verilog

Verilog也是一種硬體描述語言(HDL),用於設計和程式設計PLD。與VHDL類似,Verilog也支援併發和順序描述,使工程師和設計師能夠定義數位電路的結構和行為。

這種程式語言最常用於半導體行業,用於設計和程式設計各種數字系統。

PALASM

PALASM代表可程式設計陣列邏輯彙編器。它也是一種用於程式設計可程式設計邏輯器件(PLD)的硬體描述語言(HDL)和彙編器。在PALASM的情況下,PLD的行為、邏輯功能和結構使用文字語言格式進行描述。因此,開發人員必須編寫PALASM程式碼來描述所需的邏輯功能和互連。之後,這些程式碼被組裝成適合可程式設計邏輯器件的格式。

然而,PALASM是一種較舊的硬體描述語言,在20世紀80年代和90年代初被廣泛用於開發基於PLD的邏輯電路。

ABEL

ABEL代表高階布林表示式語言。它是一種為程式設計可程式設計邏輯器件(PLD)而開發的高階硬體描述語言。

在ABEL中,邏輯方程式、真值表和暫存器傳輸級設計描述使用易於閱讀的語法進行指定。然後,ABEL編譯器將所有這些設計描述轉換為適合程式設計所需PLD的格式。ABEL在20世紀90年代是一種非常常用的使用者友好型硬體描述語言。

CUPL

CUPL代表通用可程式設計邏輯編譯器。它也是一種用於程式設計各種PLD的硬體描述語言(HDL)和編譯器。在這種程式語言中,邏輯函式、真值表和時序邏輯指令以簡單的語法形式指定。

這種HDL語言在20世紀90年代和21世紀初也很流行,用於設計基於PLD的邏輯電路。

所有這些都是一些用於設計和程式設計可程式設計邏輯器件的重要程式語言。PALASM、ABEL和CUPL語言主要用於低複雜度的器件。而VHDL和Verilog則用於程式設計現代的高複雜度PLD。

可程式設計邏輯器件的優點

可程式設計邏輯器件(PLD)具有許多優點,使其成為數字系統設計領域的重要工具。以下是可程式設計邏輯器件的一些重要優勢:

- 可程式設計邏輯器件(PLD)易於程式設計和重新程式設計。因此,它們在設計和實現各種邏輯功能方面提供了顯著的靈活性。

- PLD允許設計定製的邏輯電路以滿足應用的特定需求。這可以透過程式設計器件的內部邏輯電路來實現。

- PLD可用於數位電路的原型設計和測試,這有助於更快地進行新產品開發。透過加速產品開發過程,PLD有助於減少硬體設計中涉及的時間和成本。

- PLD提供了一種快速且經濟高效的方式來開發中到複雜的數字邏輯電路和系統。PLD透過將大量邏輯功能和元件整合到單個器件中,有助於開發簡單、廉價且緊湊的數字系統。

- PLD還支援現代處理技術,如並行處理、流水線處理等。此功能有助於透過同時執行邏輯功能來實現高效能。

可程式設計邏輯器件的侷限性

可程式設計邏輯器件(PLD)提供了上面討論的幾個優點,但它們也有一些侷限性。以下是可程式設計邏輯器件的一些主要侷限性:

- 可程式設計邏輯器件可以設計為支援有限數量的邏輯功能和元素。因此,複雜數位電路的實現可能需要多個器件。

- PLD通常具有固定數量的輸入/輸出(I/O)引腳。此限制可能會導致連線性和與外部/外圍裝置介面方面的問題。

- PLD的程式設計需要硬體描述語言(HDL)和設計工具的知識。有時,由於意外重新程式設計或資料損壞,PLD可能會出現故障。

- PLD本身並不支援通用處理器中使用的複雜算術運算和其他高階程式設計運算。因此,開發人員必須透過定製邏輯設計來實現此類運算和功能。

可程式設計邏輯器件的應用

可程式設計邏輯器件(PLD)廣泛應用於各個領域和行業,用於設計數字邏輯電路和實現各種邏輯功能。以下是可程式設計邏輯器件的一些常見應用:

- PLD廣泛用於嵌入式系統,執行不同的即時操作,如控制、介面和資料處理。

- 在數字訊號處理領域,PLD用於設計數字濾波器、開發調變解調器演算法、執行訊號處理等。

- PLD在通訊系統中發揮著重要作用,因為它們有助於執行各種操作,如訊號路由、資料加密和解密、協議轉換等。

- 在航空航天和國防領域,PLD用於完成各種關鍵功能,如飛行控制、操作雷達系統、引導導彈、加密機密資料等。

- PLD也用於機器人和工業自動化,以控制和監控機械的操作。

- 在醫療裝置中,PLD用於自動高速資料處理、醫療資料的即時分析、患者監測等。

結論

總之,可程式設計邏輯器件是一種可以程式設計或訓練以執行特定邏輯功能的數字器件。它主要用於各種應用中的自動化和效率改進目的。

在本章中,我們解釋了PLD的基本知識、型別、優點、侷限性和應用。在下一章中,我們將探討各種可程式設計邏輯器件及其功能和特性。