- 數位電子教程

- 數位電子 - 首頁

- 數位電子基礎

- 數字系統的型別

- 訊號的型別

- 邏輯電平和脈衝波形

- 數字系統元件

- 數字邏輯運算

- 數字系統優勢

- 數制

- 數制

- 二進位制數的表示

- 二進位制運算

- 有符號二進位制運算

- 八進位制運算

- 十六進位制運算

- 補碼運算

- 進位制轉換

- 進位制轉換

- 二進位制轉十進位制

- 十進位制轉二進位制

- 二進位制轉八進位制

- 八進位制轉二進位制

- 八進位制轉十進位制

- 十進位制轉八進位制

- 十六進位制轉二進位制

- 二進位制轉十六進位制

- 十六進位制轉十進位制

- 十進位制轉十六進位制

- 八進位制轉十六進位制

- 十六進位制轉八進位制

- 二進位制編碼

- 二進位制編碼

- 8421 BCD碼

- 餘3碼

- 格雷碼

- ASCII碼

- EBCDIC碼

- 編碼轉換

- 錯誤檢測與糾錯碼

- 邏輯閘

- 邏輯閘

- 與門

- 或門

- 非門

- 通用門

- 異或門

- 異或非門

- CMOS邏輯閘

- 使用二極體電阻邏輯的或門

- 與門與或門

- 雙電平邏輯實現

- 閾值邏輯

- 布林代數

- 布林代數

- 布林代數定律

- 布林函式

- 德摩根定理

- SOP和POS形式

- POS到標準POS形式

- 最小化技術

- 卡諾圖化簡

- 三變數卡諾圖

- 四變數卡諾圖

- 五變數卡諾圖

- 六變數卡諾圖

- 無關項

- 奎因-麥克拉斯基方法

- 最小項和最大項

- 規範式和標準式

- 最大項表示

- 使用布林代數進行簡化

- 組合邏輯電路

- 數字組合電路

- 數字運算電路

- 多路複用器

- 多路複用器設計流程

- MUX通用門

- 使用4:1MUX的2變數函式

- 使用8:1MUX的3變數函式

- 多路分解器

- MUX與DEMUX

- 奇偶校驗位生成器和檢查器

- 比較器

- 編碼器

- 鍵盤編碼器

- 優先編碼器

- 譯碼器

- 算術邏輯單元

- 7段LED顯示器

- 程式碼轉換器

- 程式碼轉換器

- 二進位制轉十進位制轉換器

- 十進位制轉BCD轉換器

- BCD轉十進位制轉換器

- 二進位制轉格雷碼轉換器

- 格雷碼轉二進位制轉換器

- BCD轉餘3碼轉換器

- 餘3碼轉BCD轉換器

- 加法器

- 半加器

- 全加器

- 序列加法器

- 並行加法器

- 使用半加器的全加器

- 半加器與全加器

- 使用與非門的全加器

- 使用與非門的半加器

- 二進位制加法器-減法器

- 減法器

- 半減器

- 全減器

- 並行減法器

- 使用2個半減器的全減器

- 使用與非門的半減器

- 時序邏輯電路

- 數字時序電路

- 時鐘訊號和觸發

- 鎖存器

- 移位暫存器

- 移位暫存器應用

- 二進位制暫存器

- 雙向移位暫存器

- 計數器

- 二進位制計數器

- 非二進位制計數器

- 同步計數器設計

- 同步計數器與非同步計數器

- 有限狀態機

- 演算法狀態機

- 觸發器

- 觸發器

- 觸發器轉換

- D觸發器

- JK觸發器

- T觸發器

- SR觸發器

- 帶時鐘的SR觸發器

- 無時鐘SR觸發器

- 帶時鐘的JK觸發器

- JK到T觸發器

- SR到JK觸發器

- 觸發方法:觸發器

- 邊沿觸發觸發器

- 主從JK觸發器

- 競爭冒險現象

- A/D和D/A轉換器

- 模數轉換器

- 數模轉換器

- DAC和ADC積體電路

- 邏輯閘的實現

- 用與非門實現非門

- 用與非門實現或門

- 用與非門實現與門

- 用與非門實現或非門

- 用與非門實現異或門

- 用與非門實現異或非門

- 用或非門實現非門

- 用或非門實現或門

- 用或非門實現與門

- 用或非門實現與非門

- 用或非門實現異或門

- 用或非門實現異或非門

- 使用CMOS的與非/或非門

- 使用與非門的全減器

- 使用2:1MUX的與門

- 使用2:1MUX的或門

- 使用2:1MUX的非門

- 儲存器裝置

- 儲存器裝置

- RAM和ROM

- 快取記憶體設計

- 可程式設計邏輯器件

- 可程式設計邏輯器件

- 可程式設計邏輯陣列

- 可程式設計陣列邏輯

- 現場可程式設計門陣列

- 數字電子系列

- 數字電子系列

- CPU架構

- CPU架構

- 數位電子資源

- 數位電子 - 快速指南

- 數位電子 - 資源

- 數位電子 - 討論

演算法狀態機

每個數字系統都可以分成兩個部分。分別是資料通路(數字)電路和控制電路。資料通路電路執行諸如儲存二進位制資訊(資料)和將資料從一個系統傳輸到另一個系統的功能。而控制電路則確定數位電路的操作流程。

使用狀態圖很難描述大型狀態機的行為。為了克服這個困難,可以使用演算法狀態機(ASM)圖。ASM圖類似於流程圖。它們用於表示資料通路電路和控制電路需要執行的任務流程。

ASM圖的基本組成部分

以下是ASM圖的三個基本組成部分。

- 狀態框

- 決策框

- 條件輸出框

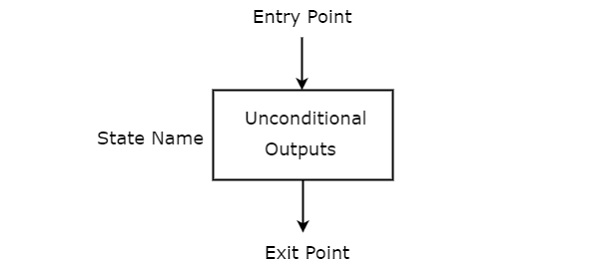

狀態框

狀態框用矩形表示。每個狀態框代表時序電路的一個狀態。狀態框的符號如下圖所示。

它有一個入口點和一個出口點。狀態的名稱放在狀態框的左側。與該狀態相對應的不受條件限制的輸出可以放在狀態框內。Moore狀態機的輸出也可以放在狀態框內。

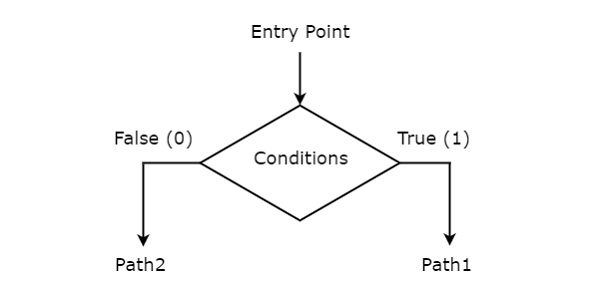

決策框

決策框用菱形表示。決策框的符號如下圖所示。

它有一個入口點和兩條出口路徑。可以在決策框內放置要檢查的輸入或布林表示式,以判斷其真假。如果條件為真,則選擇path1。否則,選擇path2。

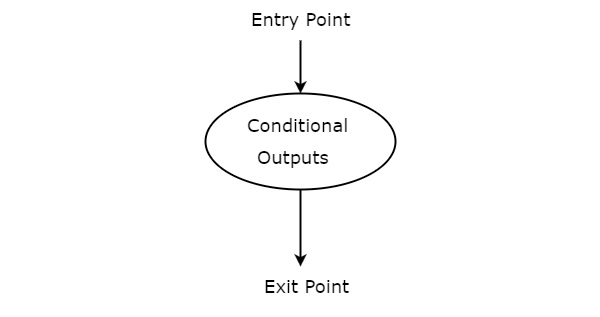

條件輸出框

條件輸出框用橢圓形表示。條件輸出框的符號如下圖所示。

它也像狀態框一樣有一個入口點和一個出口點。條件輸出可以放在狀態框內。通常,Mealy狀態機的輸出表示在條件輸出框內。因此,根據需要,我們可以正確使用上述元件繪製ASM圖。

廣告