- 8085 微處理器

- 微處理器 - 8085 架構

- 8085 引腳配置

- 定址方式和中斷

- 8085 指令集

- 多處理器配置

- 配置概述

- 8087 數值資料處理器

- I/O 介面

- I/O 介面概述

- 8279 可程式設計鍵盤

- 8257 DMA 控制器

- 微處理器有用資源

- 微處理器快速指南

- 微處理器 - 有用資源

- 微處理器 - 討論

微處理器快速指南

微處理器 - 概述

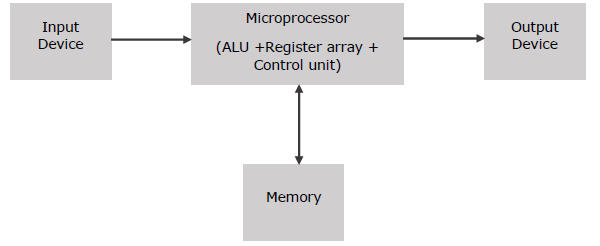

微處理器是微型計算機的控制單元,製造在一個小型晶片上,能夠執行算術邏輯單元 (ALU) 操作並與連線到它的其他裝置通訊。

微處理器由算術邏輯單元 (ALU)、暫存器陣列和控制單元組成。ALU 對從記憶體或輸入裝置接收的資料執行算術和邏輯運算。暫存器陣列由用字母(如 B、C、D、E、H、L 和累加器)標識的暫存器組成。控制單元控制計算機內的資料和指令的流程。

基本微型計算機的框圖

微處理器是如何工作的?

微處理器遵循以下順序:取指令、解碼和執行。

最初,指令按順序儲存在記憶體中。微處理器從記憶體中獲取這些指令,然後對其進行解碼並執行這些指令,直到到達 STOP 指令。之後,它將結果以二進位制形式傳送到輸出埠。在這些過程之間,暫存器儲存臨時資料,ALU 執行計算功能。

微處理器中使用的術語列表

以下是微處理器中一些常用術語的列表:

指令集 - 微處理器可以理解的指令集。

頻寬 - 單條指令中處理的位數。

時鐘速度 - 確定處理器每秒可以執行的操作次數。以兆赫茲 (MHz) 或千兆赫茲 (GHz) 表示。也稱為時鐘頻率。

字長 - 取決於內部資料匯流排、暫存器、ALU 等的寬度。8 位微處理器一次可以處理 8 位資料。字長範圍從 4 位到 64 位,具體取決於微型計算機的型別。

資料型別 - 微處理器具有多種資料型別格式,例如二進位制、BCD、ASCII、有符號數和無符號數。

微處理器的特點

以下是任何微處理器的一些最突出的特點:

經濟高效 - 微處理器芯片價格低廉,因此成本低。

尺寸小巧 - 微處理器晶片尺寸小,便於攜帶。

低功耗 - 微處理器採用金氧半導體技術製造,功耗低。

通用性強 - 微處理器用途廣泛,可以透過配置軟體程式在許多應用程式中使用相同的晶片。

可靠性高 - 微處理器中積體電路的故障率非常低,因此非常可靠。

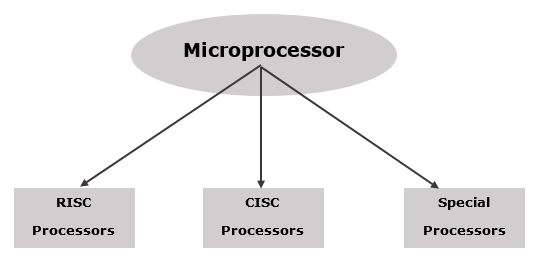

微處理器 - 分類

微處理器可分為三類:

精簡指令集計算機 (RISC) 處理器

RISC 代表精簡指令集計算機。它旨在透過簡化計算機的指令集來減少執行時間。使用 RISC 處理器,每條指令只需要一個時鐘週期即可執行,從而實現統一的執行時間。但這降低了效率,因為程式碼行數更多,因此需要更多 RAM 來儲存指令。編譯器也必須做更多工作才能將高階語言指令轉換為機器碼。

一些 RISC 處理器包括:

- Power PC:601、604、615、620

- DEC Alpha:210642、211066、21068、21164

- MIPS:TS (R10000) RISC 處理器

- PA-RISC:HP 7100LC

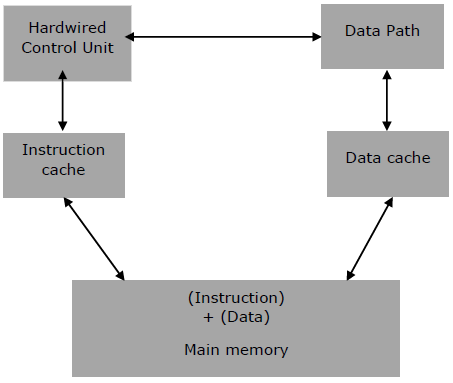

RISC 架構

RISC 微處理器架構使用高度最佳化的指令集。由於其功耗效率,它被用於蘋果 iPod 等行動式裝置中。

RISC 的特點

RISC 處理器的主要特點如下:

它包含簡單的指令。

它支援各種資料型別格式。

它使用簡單的定址模式和固定長度指令進行流水線處理。

它支援在任何上下文中使用暫存器。

單週期執行時間。

“LOAD”和“STORE”指令用於訪問記憶體位置。

它包含大量暫存器。

它包含較少數量的電晶體。

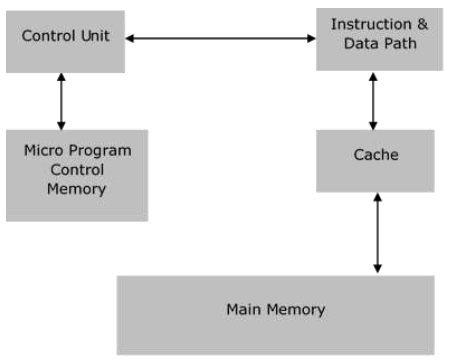

複雜指令集計算機 (CISC) 處理器

CISC 代表複雜指令集計算機。它旨在最大限度地減少每個程式的指令數量,而忽略每條指令的週期數。重點是將複雜指令直接嵌入到硬體中。

編譯器只需要做很少的工作就能將高階語言轉換為組合語言/機器碼,因為程式碼長度相對較短,所以只需要很少的 RAM 來儲存指令。

一些 CISC 處理器包括:

- IBM 370/168

- VAX 11/780

- Intel 80486

CISC 架構

其架構旨在降低記憶體成本,因為較大的程式需要更多儲存空間,導致更高的記憶體成本。為了解決這個問題,可以透過將多個操作嵌入到單個指令中來減少每個程式的指令數量。

CISC 的特點

- 各種定址模式。

- 大量指令。

- 可變長度的指令格式。

- 執行一條指令可能需要多個週期。

- 指令解碼邏輯複雜。

- 一條指令需要支援多種定址模式。

專用處理器

這些處理器是為某些特殊用途而設計的。下面簡要介紹了一些專用處理器:

協處理器

協處理器是一種專門設計的微處理器,它可以處理其特定功能的速度比普通微處理器快很多倍。

例如 - 數學協處理器。

一些 Intel 數學協處理器包括:

- 8087 - 與 8086 一起使用

- 80287 - 與 80286 一起使用

- 80387 - 與 80386 一起使用

輸入/輸出處理器

它是一種專門設計的微處理器,具有自己的本地記憶體,用於在最少 CPU 參與的情況下控制 I/O 裝置。

例如:

- DMA(直接記憶體訪問)控制器

- 鍵盤/滑鼠控制器

- 圖形顯示控制器

- SCSI 埠控制器

超立方體 (Transputer)

超立方體是一種專門設計的微處理器,具有自己的本地記憶體,並具有連線一個超立方體到另一個超立方體以進行處理器間通訊的鏈路。它於 1980 年由 Inmos 首次設計,目標是利用 VLSI 技術。

超立方體可以用作單處理器系統,也可以連線到外部鏈路,這降低了建設成本並提高了效能。

例如 - 16 位 T212、32 位 T425、浮點 (T800、T805 和 T9000) 處理器。

數字訊號處理器 (DSP)

此處理器專門設計用於將模擬訊號處理成數字形式。這是透過定期取樣電壓水平並將該時刻的電壓轉換為數字形式來完成的。此過程由稱為模數轉換器、A 到 D 轉換器或 ADC 的電路執行。

DSP 包含以下元件:

程式儲存器 - 它儲存 DSP 用於處理資料的程式。

資料儲存器 - 它儲存要處理的資訊。

計算引擎 - 它執行數學處理,從程式儲存器訪問程式,從資料儲存器訪問資料。

輸入/輸出 - 它連線到外部世界。

其應用包括:

- 聲音和音樂合成

- 音訊和影片壓縮

- 影片訊號處理

- 2D 和 3D 圖形加速。

例如 - 德州儀器的 TMS 320 系列,例如 TMS 320C40、TMS320C50。

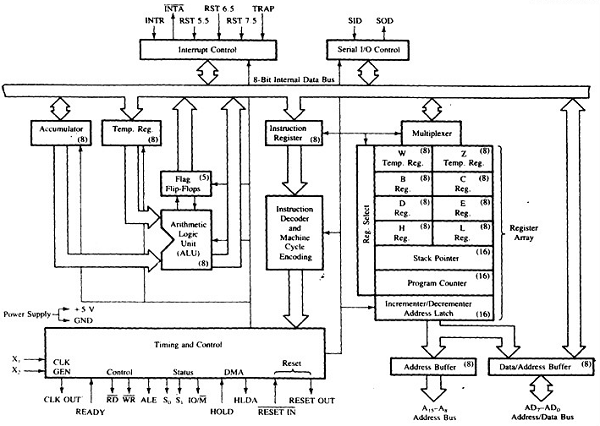

微處理器 - 8085 架構

8085 讀作“八十-八十五”微處理器。它是英特爾於 1977 年使用 NMOS 技術設計的 8 位微處理器。

它具有以下配置:

- 8 位資料匯流排

- 16 位地址匯流排,最多可定址 64KB

- 16 位程式計數器

- 16 位堆疊指標

- 六個 8 位暫存器成對排列:BC、DE、HL

- 需要 +5V 電源才能以 3.2 MHz 單相時鐘執行

它用於洗衣機、微波爐、行動電話等。

8085 微處理器 - 功能單元

8085 包含以下功能單元:

累加器

這是一個 8 位暫存器,用於執行算術、邏輯、I/O 和 LOAD/STORE 操作。它連線到內部資料匯流排和 ALU。

算術邏輯單元

顧名思義,它對 8 位資料執行算術和邏輯運算,如加法、減法、AND、OR 等。

通用暫存器

8085 處理器中有 6 個通用暫存器,即 B、C、D、E、H 和 L。每個暫存器可以儲存 8 位資料。

這些暫存器可以成對工作以儲存 16 位資料,其配對組合類似於 B-C、D-E 和 H-L。

程式計數器

這是一個 16 位暫存器,用於儲存要執行的下一條指令的記憶體地址位置。每執行一條指令,微處理器都會遞增程式計數器,以便程式計數器指向將要執行的下一條指令的記憶體地址。

堆疊指標

它也是一個 16 位暫存器,像堆疊一樣工作,在 push 和 pop 操作期間始終遞增/遞減 2。

臨時暫存器

這是一個 8 位暫存器,它儲存算術和邏輯運算的臨時資料。

標誌暫存器

這是一個 8 位暫存器,具有五個 1 位觸發器,根據儲存在累加器中的結果儲存 0 或 1。

這五個觸發器是:

- 符號 (S)

- 零 (Z)

- 輔助進位 (AC)

- 奇偶校驗 (P)

- 進位 (C)

其位位置如下表所示:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| S | Z | AC | P | CY |

指令暫存器和解碼器

這是一個 8 位暫存器。當從記憶體中獲取指令時,它儲存在指令暫存器中。指令解碼器解碼指令暫存器中存在的資訊。

定時和控制單元

它為微處理器提供定時和控制訊號以執行操作。以下是控制外部和內部電路的定時和控制訊號:

- 控制訊號:READY,RD’,WR’,ALE

- 狀態訊號:S0,S1,IO/M’

- DMA訊號:HOLD,HLDA

- 復位訊號:RESET IN,RESET OUT

中斷控制

顧名思義,它控制程序中的中斷。當微處理器正在執行主程式,並且發生中斷時,微處理器將控制從主程式轉移到處理傳入的請求。請求完成後,控制返回主程式。

8085微處理器有5箇中斷訊號:INTR,RST 7.5,RST 6.5,RST 5.5,TRAP。

序列輸入/輸出控制

它使用這兩個指令控制序列資料通訊:SID(序列輸入資料)和SOD(序列輸出資料)。

地址緩衝器和地址資料緩衝器

將堆疊指標和程式計數器中儲存的內容載入到地址緩衝器和地址資料緩衝器中,以與CPU通訊。記憶體和I/O晶片連線到這些總線上;CPU可以與記憶體和I/O晶片交換所需的資料。

地址匯流排和資料匯流排

資料匯流排承載要儲存的資料。它是雙向的,而地址匯流排承載資料應該儲存到的位置,它是單向的。它用於傳輸資料和地址I/O裝置。

8085架構

我們嘗試使用以下影像描述8085的架構:

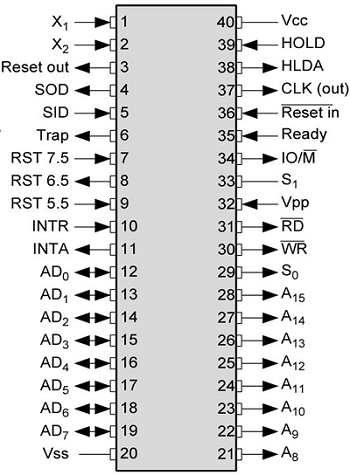

微處理器 - 8085引腳配置

下圖顯示了8085微處理器的引腳圖:

8085微處理器的引腳可以分為七組:

地址匯流排

A15-A8,它承載記憶體/IO地址的最高有效8位。

資料匯流排

AD7-AD0,它承載最低有效8位地址和資料匯流排。

控制和狀態訊號

這些訊號用於識別操作的性質。有3個控制訊號和3個狀態訊號。

三個控制訊號是RD、WR和ALE。

RD - 此訊號表示所選的IO或記憶體裝置將被讀取,並已準備好接收資料匯流排上可用的資料。

WR - 此訊號表示資料匯流排上的資料將被寫入選定的記憶體或IO位置。

ALE - 這是微處理器啟動新操作時產生的正脈衝。當脈衝變高時,它表示地址。當脈衝變低時,它表示資料。

三個狀態訊號是IO/M、S0和S1。

IO/M

此訊號用於區分IO和記憶體操作,即當它為高時表示IO操作,當它為低時表示記憶體操作。

S1和S0

這些訊號用於識別當前操作的型別。

電源

有2個電源訊號 - VCC和VSS。VCC表示+5v電源,VSS表示接地訊號。

時鐘訊號

有3個時鐘訊號,即X1、X2、CLK OUT。

X1,X2 - 晶體(RC,LC網路)連線在這兩個引腳上,用於設定內部時鐘發生器的頻率。此頻率在內部除以2。

CLK OUT - 此訊號用作與微處理器連線的裝置的系統時鐘。

中斷和外部啟動訊號

中斷是由外部裝置生成的訊號,請求微處理器執行任務。有5箇中斷訊號,即TRAP、RST 7.5、RST 6.5、RST 5.5和INTR。我們將在中斷部分詳細討論中斷。

INTA - 這是一箇中斷確認訊號。

RESET IN - 此訊號用於透過將程式計數器設定為零來複位微處理器。

RESET OUT - 當微處理器復位時,此訊號用於復位所有連線的裝置。

READY - 此訊號表示裝置已準備好傳送或接收資料。如果READY為低,則CPU必須等待READY變高。

HOLD - 此訊號表示另一個主裝置正在請求使用地址和資料匯流排。

HLDA(HOLD Acknowledge) - 它表示CPU已收到HOLD請求,它將在下一個時鐘週期釋放匯流排。在HOLD訊號移除後,HLDA設定為低。

序列I/O訊號

有2個序列訊號,即SID和SOD,這些訊號用於序列通訊。

SOD(序列輸出資料線) - 如SIM指令指定的,輸出SOD被設定/復位。

SID(序列輸入資料線) - 每當執行RIM指令時,此線路上的資料就會載入到累加器中。

8085定址模式和中斷

現在讓我們討論8085微處理器的定址模式。

8085中的定址模式

這些指令用於在不更改內容的情況下將資料從一個暫存器傳輸到另一個暫存器,從記憶體到暫存器,以及從暫存器到記憶體。8085中的定址模式分為5組:

立即定址模式

在這種模式下,8/16位資料在指令本身中作為其運算元之一指定。**例如:**MVI K, 20F:表示將20F複製到暫存器K。

暫存器定址模式

在這種模式下,資料從一個暫存器複製到另一個暫存器。**例如:**MOV K, B:表示暫存器B中的資料被複制到暫存器K。

直接定址模式

在這種模式下,資料直接從給定地址複製到暫存器。**例如:**LDB 5000K:表示地址5000K處的資料被複制到暫存器B。

間接定址模式

在這種模式下,資料透過使用暫存器指向的地址從一個暫存器傳輸到另一個暫存器。**例如:**MOV K, B:表示資料從暫存器指向的記憶體地址傳輸到暫存器K。

隱含定址模式

此模式不需要任何運算元;資料由操作碼本身指定。**例如:**CMP。

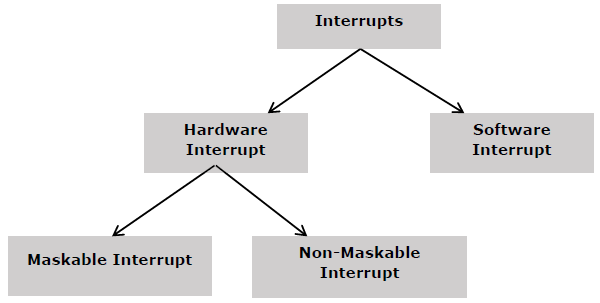

8085中的中斷

中斷是由外部裝置生成的訊號,請求微處理器執行任務。有5箇中斷訊號,即TRAP、RST 7.5、RST 6.5、RST 5.5和INTR。

根據其引數,中斷分為以下幾組:

向量中斷 - 在這種型別的中斷中,中斷地址為處理器所知。**例如:**RST7.5,RST6.5,RST5.5,TRAP。

非向量中斷 - 在這種型別的中斷中,中斷地址對處理器未知,因此需要由裝置外部發送中斷地址來執行中斷。**例如:**INTR。

可遮蔽中斷 - 在這種型別的中斷中,我們可以透過向程式寫入一些指令來停用中斷。**例如:**RST7.5,RST6.5,RST5.5。

不可遮蔽中斷 - 在這種型別的中斷中,我們不能透過向程式寫入一些指令來停用中斷。**例如:**TRAP。

軟體中斷 - 在這種型別的中斷中,程式設計師必須向程式新增指令來執行中斷。8085中有8個軟體中斷,即RST0、RST1、RST2、RST3、RST4、RST5、RST6和RST7。

硬體中斷 - 8085中有5箇中斷引腳用作硬體中斷,即TRAP、RST7.5、RST6.5、RST5.5、INTA。

注意 - NTA不是中斷,它被微處理器用於傳送確認。TRAP具有最高優先順序,然後是RST7.5,依此類推。

中斷服務程式(ISR)

一個小的程式或例程,當執行時,為相應的中斷源提供服務,稱為ISR。

TRAP

這是一個不可遮蔽中斷,在所有中斷中具有最高的優先順序。預設情況下,它被啟用,直到它被確認。如果失敗,它將作為ISR執行並將資料傳送到備份記憶體。此中斷將控制轉移到0024H位置。

RST7.5

這是一個可遮蔽中斷,在所有中斷中具有第二高的優先順序。當執行此中斷時,處理器將PC暫存器的內容儲存到堆疊中,並跳轉到003CH地址。

RST 6.5

這是一個可遮蔽中斷,在所有中斷中具有第三高的優先順序。當執行此中斷時,處理器將PC暫存器的內容儲存到堆疊中,並跳轉到0034H地址。

RST 5.5

這是一個可遮蔽中斷。當執行此中斷時,處理器將PC暫存器的內容儲存到堆疊中,並跳轉到002CH地址。

INTR

這是一個可遮蔽中斷,在所有中斷中具有最低的優先順序。可以透過復位微處理器來停用它。

當INTR訊號變高時,可能會發生以下事件:

微處理器在執行每條指令期間都會檢查INTR訊號的狀態。

當INTR訊號為高時,微處理器將完成其當前指令併發送有效低中斷確認訊號。

當接收到指令時,微處理器將儲存堆疊上下一條指令的地址並執行接收到的指令。

微處理器 - 8085指令集

讓我們來看一下8085微處理器的程式設計。

指令集是執行某些任務的指令程式碼。它分為五類。

| 序號 | 指令和描述 |

|---|---|

| 1 | 控制指令

下表顯示了控制指令及其含義的列表。 |

| 2 | 邏輯指令

下表顯示了邏輯指令及其含義的列表。 |

| 3 | 分支指令

下表顯示了分支指令及其含義的列表。 |

| 4 | 算術指令

下表顯示了算術指令及其含義的列表。 |

| 5 | 資料傳輸指令

下表顯示了資料傳輸指令及其含義的列表。 |

8085 – 演示程式

現在,讓我們來看一些使用上述指令的程式演示:

新增兩個8位數字

編寫一個程式,將3005H和3006H記憶體位置的資料相加,並將結果儲存到3007H記憶體位置。

問題演示 -

(3005H) = 14H (3006H) = 89H

結果 -

14H + 89H = 9DH

程式程式碼可以這樣編寫:

LXI H 3005H : "HL points 3005H" MOV A, M : "Getting first operand" INX H : "HL points 3006H" ADD M : "Add second operand" INX H : "HL points 3007H" MOV M, A : "Store result at 3007H" HLT : "Exit program"

交換記憶體位置

編寫一個程式來交換5000M和6000M記憶體位置的資料。

LDA 5000M : "Getting the contents at5000M location into accumulator" MOV B, A : "Save the contents into B register" LDA 6000M : "Getting the contents at 6000M location into accumulator" STA 5000M : "Store the contents of accumulator at address 5000M" MOV A, B : "Get the saved contents back into A register" STA 6000M : "Store the contents of accumulator at address 6000M"

將數字按升序排列

編寫一個程式,將從3000H記憶體地址開始的前10個數字按升序排列。

MVI B, 09 :"Initialize counter" START :"LXI H, 3000H: Initialize memory pointer" MVI C, 09H :"Initialize counter 2" BACK: MOV A, M :"Get the number" INX H :"Increment memory pointer" CMP M :"Compare number with next number" JC SKIP :"If less, don’t interchange" JZ SKIP :"If equal, don’t interchange" MOV D, M MOV M, A DCX H MOV M, D INX H :"Interchange two numbers" SKIP:DCR C :"Decrement counter 2" JNZ BACK :"If not zero, repeat" DCR B :"Decrement counter 1" JNZ START HLT :"Terminate program execution"

微處理器 - 8086 概述

8086微處理器是英特爾於1976年設計的8085微處理器的增強版。它是一個16位微處理器,具有20條地址線和16條資料線,可提供高達1MB的儲存空間。它包含強大的指令集,可以輕鬆地執行乘法和除法等操作。

它支援兩種操作模式,即最大模式和最小模式。最大模式適用於具有多個處理器的系統,最小模式適用於具有單個處理器的系統。

8086的特性

8086微處理器的最顯著特性如下:

它有一個指令佇列,能夠從記憶體中儲存六個指令位元組,從而加快處理速度。

它是第一個具有16位ALU、16位暫存器、內部資料匯流排和16位外部資料匯流排的16位處理器,從而加快了處理速度。

它根據工作頻率有3個版本:

8086 → 5MHz

8086-2 → 8MHz

(c)8086-1 → 10 MHz

它使用兩個階段的流水線,即取指階段和執行階段,這提高了效能。

取指令階段可以預取最多 6 個位元組的指令並將它們儲存在佇列中。

執行階段執行這些指令。

它具有 256 個向量中斷。

它由 29,000 個電晶體組成。

8085 和 8086 微處理器比較

大小 - 8085 是 8 位微處理器,而 8086 是 16 位微處理器。

地址匯流排 - 8085 具有 16 位地址匯流排,而 8086 具有 20 位地址匯流排。

記憶體 - 8085 可以訪問最多 64KB,而 8086 可以訪問最多 1MB 的記憶體。

指令 - 8085 沒有指令佇列,而 8086 有指令佇列。

流水線 - 8085 不支援流水線架構,而 8086 支援流水線架構。

I/O - 8085 可以定址 2^8 = 256 個 I/O,而 8086 可以訪問 2^16 = 65,536 個 I/O。

成本 - 8085 的成本較低,而 8086 的成本較高。

8086 架構

下圖顯示了 8086 微處理器的架構 -

微處理器 - 8086 功能單元

8086 微處理器分為兩個功能單元,即EU(執行單元)和BIU(匯流排介面單元)。

EU(執行單元)

執行單元向 BIU 指示從哪裡取資料,然後解碼並執行這些指令。其功能是使用指令解碼器和 ALU 控制資料操作。如上圖所示,EU 與系統匯流排沒有直接連線,它透過 BIU 對資料執行操作。

現在讓我們討論 8086 微處理器的功能部件。

ALU

它處理所有算術和邏輯運算,例如 +、-、×、/、OR、AND、NOT 運算。

標誌暫存器

這是一個 16 位暫存器,其行為類似於觸發器,即它根據累加器中儲存的結果改變其狀態。它有 9 個標誌,分為兩組 - 條件標誌和控制標誌。

條件標誌

它表示最後執行的算術或邏輯指令的結果。以下是條件標誌的列表 -

進位標誌 - 此標誌指示算術運算的溢位情況。

輔助進位標誌 - 當在 ALU 執行運算時,它會導致從低位 nibble(即 D0 – D3)到高位 nibble(即 D4 – D7)的進位/借位,則設定此標誌,即 D3 位到 D4 的進位是 AF 標誌。處理器使用此標誌執行二進位制到 BCD 的轉換。

奇偶標誌 - 此標誌用於指示結果的奇偶性,即當結果的低 8 位包含偶數個 1 時,則設定奇偶標誌。對於奇數個 1,奇偶標誌被複位。

零標誌 - 當算術或邏輯運算的結果為零時,此標誌設定為 1,否則設定為 0。

符號標誌 - 此標誌儲存結果的符號,即當操作的結果為負時,符號標誌設定為 1,否則設定為 0。

溢位標誌 - 此標誌表示系統容量超過時的結果。

控制標誌

控制標誌控制執行單元的操作。以下是控制標誌的列表 -

陷阱標誌 - 它用於單步控制,並允許使用者一次執行一條指令進行除錯。如果設定了它,則程式可以以單步模式執行。

中斷標誌 - 它是一箇中斷啟用/停用標誌,即用於允許/禁止程式中斷。對於中斷啟用狀態,它設定為 1;對於中斷停用狀態,它設定為 0。

方向標誌 - 它用於字串操作。顧名思義,當它被設定時,字串位元組從較高的記憶體地址訪問到較低的記憶體地址,反之亦然。

通用暫存器

有 8 個通用暫存器,即 AH、AL、BH、BL、CH、CL、DH 和 DL。這些暫存器可以單獨用於儲存 8 位資料,也可以成對使用以儲存 16 位資料。有效的暫存器對是 AH 和 AL、BH 和 BL、CH 和 CL 以及 DH 和 DL。它們分別稱為 AX、BX、CX 和 DX。

AX 暫存器 - 也稱為累加器暫存器。它用於儲存算術運算的運算元。

BX 暫存器 - 用作基址暫存器。它用於儲存資料段內記憶體區域的起始基址。

CX 暫存器 - 稱為計數器。它在迴圈指令中用於儲存迴圈計數器。

DX 暫存器 - 此暫存器用於儲存 I/O 指令的 I/O 埠地址。

堆疊指標暫存器

這是一個 16 位暫存器,它儲存從段的起始位置到記憶體位置的地址,最近儲存在堆疊上的字就在該位置。

BIU(匯流排介面單元)

BIU 負責 EU 在總線上進行的所有資料和地址傳輸,例如傳送地址、從記憶體中取指令、從埠和記憶體中讀取資料以及將資料寫入埠和記憶體。EU 與系統匯流排沒有直接連線,因此這可以透過 BIU 實現。EU 和 BIU 透過內部匯流排連線。

它具有以下功能部件 -

指令佇列 - BIU 包含指令佇列。BIU 獲取多達 6 個位元組的下一條指令並將它們儲存在指令佇列中。當 EU 執行指令並準備好其下一條指令時,它只需從指令佇列中讀取指令,從而提高執行速度。

在執行當前指令的同時獲取下一條指令稱為流水線。

段暫存器 - BIU 有 4 個段匯流排,即 CS、DS、SS 和 ES。它儲存記憶體中指令和資料的地址,處理器使用這些地址來訪問記憶體位置。它還包含 1 個指標暫存器 IP,它儲存 EU 要執行的下一條指令的地址。

CS - 代表程式碼段。它用於定址記憶體中程式碼段中的記憶體位置,可執行程式儲存在該位置。

DS - 代表資料段。它包含程式使用的資料,並透過偏移地址或儲存偏移地址的其他暫存器的內容在資料段中被訪問。

SS - 代表堆疊段。它處理在執行期間儲存資料和地址的記憶體。

ES - 代表附加段。ES 是附加資料段,字串使用它來儲存額外的目標資料。

指令指標 - 這是一個 16 位暫存器,用於儲存要執行的下一條指令的地址。

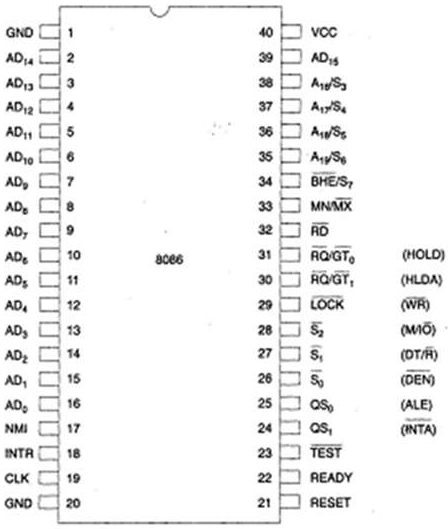

微處理器 - 8086 引腳配置

8086 是第一個採用 40 引腳 DIP(雙列直插式封裝)晶片的 16 位微處理器。現在讓我們詳細討論 8086 微處理器的引腳配置。

8086 引腳圖

以下是 8086 微處理器的引腳圖 -

現在讓我們詳細討論這些訊號 -

電源和頻率訊號

它在 VCC 引腳 40 使用 5V 直流電源,並在 VSS 引腳 1 和 20 使用接地用於其操作。

時鐘訊號

時鐘訊號透過引腳 19 提供。它為處理器的操作提供時序。其頻率對於不同的版本是不同的,即 5MHz、8MHz 和 10MHz。

地址/資料匯流排

AD0-AD15。這些是 16 位地址/資料匯流排。AD0-AD7 傳輸低位位元組資料,AD8-AD15 傳輸高位位元組資料。在第一個時鐘週期期間,它傳輸 16 位地址,之後它傳輸 16 位資料。

地址/狀態匯流排

A16-A19/S3-S6。這些是 4 位地址/狀態匯流排。在第一個時鐘週期期間,它傳輸 4 位地址,之後它傳輸狀態訊號。

S7/BHE

BHE 代表匯流排高位啟用。它位於引腳 34,用於指示使用資料匯流排 D8-D15 傳輸資料。此訊號在第一個時鐘週期期間為低電平,之後它處於活動狀態。

讀取($\overline{RD}$)

它位於引腳 32,用於讀取操作的讀取訊號。

就緒

它位於引腳 22。它是來自 I/O 裝置的資料傳輸確認訊號。它是一個高電平有效訊號。當它為高電平時,表示裝置已準備好傳輸資料。當它為低電平時,表示等待狀態。

復位

它位於引腳 21,用於重新啟動執行。它會導致處理器立即終止其當前活動。此訊號在前 4 個時鐘週期內為高電平以復位微處理器。

INTR

它位於引腳 18。這是一箇中斷請求訊號,在每條指令的最後一個時鐘週期對其進行取樣以確定處理器是否將其視為中斷。

NMI

代表非遮蔽中斷,位於引腳 17。它是一個邊沿觸發的輸入,會導致向微處理器發出中斷請求。

$\overline{TEST}$

此訊號類似於等待狀態,位於引腳 23。當此訊號為高電平時,處理器必須等待空閒狀態,否則執行繼續。

MN/$\overline{MX}$

代表最小/最大,位於引腳 33。它指示處理器要以何種模式執行;當它為高電平時,它以最小模式工作,反之亦然。

INTA

它是一箇中斷確認訊號,位於引腳 24。當微處理器接收到此訊號時,它會確認中斷。

ALE

代表地址啟用鎖存器,位於引腳 25。每次處理器開始任何操作時都會產生一個正脈衝。此訊號指示地址/資料線上有效地址的可用性。

DEN

代表資料啟用,位於引腳 26。它用於啟用收發器 8286。收發器是一個用於將資料與地址/資料匯流排分開的裝置。

DT/R

代表資料傳輸/接收訊號,位於引腳 27。它決定資料透過收發器的流動方向。當它為高電平時,資料被傳輸出去,反之亦然。

M/IO

此訊號用於區分儲存器和I/O操作。高電平時表示I/O操作,低電平時表示儲存器操作。它位於28引腳。

WR

代表寫訊號,位於29引腳。根據M/IO訊號的狀態,它用於將資料寫入記憶體或輸出裝置。

HLDA

代表保持確認訊號,位於30引腳。此訊號確認HOLD訊號。

HOLD

此訊號指示處理器外部裝置正在請求訪問地址/資料匯流排。它位於31引腳。

QS1和QS0

這些是佇列狀態訊號,位於24和25引腳。這些訊號提供指令佇列的狀態。其狀態如下表所示:

| QS0 | QS1 | 狀態 |

|---|---|---|

| 0 | 0 | 無操作 |

| 0 | 1 | 佇列中操作碼的第一個位元組 |

| 1 | 0 | 清空佇列 |

| 1 | 1 | 佇列中的後續位元組 |

S0, S1, S2

這些是狀態訊號,提供操作狀態,由匯流排控制器8288用於生成記憶體和I/O控制訊號。它們位於26、27和28引腳。下表顯示了它們的狀態:

| S2 | S1 | S0 | 狀態 |

|---|---|---|---|

| 0 | 0 | 0 | 中斷確認 |

| 0 | 0 | 1 | I/O讀 |

| 0 | 1 | 0 | I/O寫 |

| 0 | 1 | 1 | 暫停 |

| 1 | 0 | 0 | 操作碼提取 |

| 1 | 0 | 1 | 記憶體讀 |

| 1 | 1 | 0 | 記憶體寫 |

| 1 | 1 | 1 | 被動 |

LOCK

當此訊號啟用時,它指示其他處理器不要請求CPU釋放系統匯流排。它透過在任何指令上使用LOCK字首來啟用,位於29引腳。

RQ/GT1和RQ/GT0

這些是請求/授權訊號,由其他處理器用於請求CPU釋放系統匯流排。當CPU收到訊號時,它會發送確認。RQ/GT0優先順序高於RQ/GT1。

微處理器 - 8086指令集

8086微處理器支援8種類型的指令:

- 資料傳輸指令

- 算術指令

- 位操作指令

- 字串指令

- 程式執行轉移指令(分支和迴圈指令)

- 處理器控制指令

- 迭代控制指令

- 中斷指令

現在讓我們詳細討論這些指令集。

資料傳輸指令

這些指令用於將資料從源運算元傳輸到目標運算元。以下是此組中的指令列表:

傳輸字的指令

MOV − 用於將位元組或字從提供的源複製到提供的目標。

PUSH − 用於將字壓入堆疊頂部。

POP − 用於將字從堆疊頂部彈出到指定位置。

PUSHA − 用於將所有暫存器壓入堆疊。

POPA − 用於將字從堆疊彈出到所有暫存器。

XCHG − 用於交換兩個位置的資料。

XLAT − 用於使用記憶體中的錶轉換AL中的位元組。

輸入和輸出埠傳輸指令

IN − 用於將位元組或字從指定埠讀取到累加器。

OUT − 用於將位元組或字從累加器傳送到指定埠。

傳輸地址的指令

LEA − 用於將運算元的地址載入到指定的暫存器。

LDS − 用於從記憶體載入DS暫存器和其他指定的暫存器。

LES − 用於從記憶體載入ES暫存器和其他指定的暫存器。

傳輸標誌暫存器的指令

LAHF − 用於將標誌暫存器的低位元組載入到AH中。

SAHF − 用於將AH暫存器儲存到標誌暫存器的低位元組。

PUSHF − 用於將標誌暫存器複製到堆疊頂部。

POPF − 用於將堆疊頂部的字複製到標誌暫存器。

算術指令

這些指令用於執行算術運算,如加法、減法、乘法、除法等。

以下是此組中的指令列表:

執行加法的指令

ADD − 用於將提供的位元組加到位元組/字或字加到字。

ADC − 用於帶進位的加法。

INC − 用於將提供的位元組/字加1。

AAA − 用於加法後調整ASCII碼。

DAA − 用於加法/減法運算後調整十進位制數。

執行減法的指令

SUB − 用於從位元組/字中減去位元組或從字中減去字。

SBB − 用於帶借位的減法。

DEC − 用於將提供的位元組/字減1。

NEG − 用於反轉提供的位元組/字的每一位並加1/求補碼。

CMP − 用於比較兩個提供的位元組/字。

AAS − 用於減法後調整ASCII碼。

DAS − 用於減法後調整十進位制數。

執行乘法的指令

MUL − 用於將無符號位元組乘以位元組/字乘以字。

IMUL − 用於將有符號位元組乘以位元組/字乘以字。

AAM − 用於乘法後調整ASCII碼。

執行除法的指令

DIV − 用於將無符號字除以位元組或將無符號雙字除以字。

IDIV − 用於將有符號字除以位元組或將有符號雙字除以字。

AAD − 用於除法後調整ASCII碼。

CBW − 用於用低位元組的符號位的副本填充字的高位元組。

CWD − 用於用低字的符號位填充雙字的高字。

位操作指令

這些指令用於執行涉及資料位的操作,即邏輯、移位等操作。

以下是此組中的指令列表:

執行邏輯運算的指令

NOT − 用於反轉位元組或字的每一位。

AND − 用於將位元組/字中的每一位與另一個位元組/字中的對應位相加。

OR − 用於將位元組/字中的每一位與另一個位元組/字中的對應位相乘。

XOR − 用於對位元組/字中的每一位與另一個位元組/字中的對應位執行異或運算。

TEST − 用於將運算元相加以更新標誌,而不會影響運算元。

執行移位操作的指令

SHL/SAL − 用於將位元組/字的位向左移動並將零(S)放入最低有效位。

SHR − 用於將位元組/字的位向右移動並將零(S)放入最高有效位。

SAR − 用於將位元組/字的位向右移動並將舊的最高有效位複製到新的最高有效位。

執行旋轉操作的指令

ROL − 用於將位元組/字的位向左旋轉,即最高有效位到最低有效位,以及到進位標誌[CF]。

ROR − 用於將位元組/字的位向右旋轉,即最低有效位到最高有效位,以及到進位標誌[CF]。

RCR − 用於將位元組/字的位向右旋轉,即最低有效位到CF,以及CF到最高有效位。

RCL − 用於將位元組/字的位向左旋轉,即最高有效位到CF,以及CF到最低有效位。

字串指令

字串是一組位元組/字,它們的記憶體總是按順序分配的。

以下是此組中的指令列表:

REP − 用於重複給定的指令,直到CX ≠ 0。

REPE/REPZ − 用於重複給定的指令,直到CX = 0或零標誌ZF = 1。

REPNE/REPNZ − 用於重複給定的指令,直到CX = 0或零標誌ZF = 0。

MOVS/MOVSB/MOVSW − 用於將位元組/字從一個字串移動到另一個字串。

COMPS/COMPSB/COMPSW − 用於比較兩個字串的位元組/字。

INS/INSB/INSW − 用於將I/O埠的字串/位元組/字輸入到提供的記憶體位置。

OUTS/OUTSB/OUTSW − 用於將提供的記憶體位置的字串/位元組/字輸出到I/O埠。

SCAS/SCASB/SCASW − 用於掃描字串並將它的位元組與AL中的位元組或字串字與AX中的字進行比較。

LODS/LODSB/LODSW − 用於將字串位元組儲存到AL中或將字串字儲存到AX中。

程式執行轉移指令(分支和迴圈指令)

這些指令用於在執行期間轉移/分支指令。它包括以下指令:

在執行期間無條件轉移指令的指令:

CALL − 用於呼叫過程並將它們的返回地址儲存到堆疊。

RET − 用於從過程返回到主程式。

JMP − 用於跳轉到提供的地址以繼續執行下一條指令。

在執行期間根據某些條件轉移指令的指令:

JA/JNBE − 如果高於/不低於/等於指令滿足條件則跳轉。

JAE/JNB − 如果高於/不低於指令滿足條件則跳轉。

JBE/JNA − 如果低於/等於/不高於指令滿足條件則跳轉。

JC − 如果進位標誌CF = 1則跳轉。

JE/JZ − 如果相等/零標誌ZF = 1則跳轉。

JG/JNLE − 如果大於/不小於/等於指令滿足條件則跳轉。

JGE/JNL − 如果大於/等於/不小於指令滿足條件則跳轉。

JL/JNGE − 如果小於/不大於/等於指令滿足條件則跳轉。

JLE/JNG − 如果小於/等於/不大於指令滿足條件則跳轉。

JNC − 如果沒有進位標誌(CF = 0)則跳轉。

JNE/JNZ − 如果不相等/零標誌ZF = 0則跳轉。

JNO − 如果沒有溢位標誌OF = 0則跳轉。

JNP/JPO − 如果沒有奇偶校驗/奇數奇偶校驗PF = 0則跳轉。

JNS − 如果沒有符號SF = 0則跳轉。

JO − 如果溢位標誌OF = 1則跳轉。

JP/JPE − 如果奇偶校驗/偶數奇偶校驗PF = 1則跳轉。

JS − 如果符號標誌SF = 1則跳轉。

處理器控制指令

這些指令用於透過設定/重置標誌值來控制處理器操作。

以下是此組中的指令:

STC − 用於將進位標誌CF設定為1。

CLC − 用於清除/重置進位標誌CF為0。

CMC − 用於對進位標誌CF的狀態取反。

STD − 用於將方向標誌DF設定為1。

CLD − 用於清除/重置方向標誌DF為0。

STI − 用於將中斷允許標誌設定為1,即允許INTR輸入。

CLI − 用於將中斷允許標誌清零,即停用 INTR 輸入。

迭代控制指令

這些指令用於執行給定指令多次。以下是此組下的指令列表:

LOOP − 用於迴圈執行一組指令,直到條件滿足,即 CX = 0

LOOPE/LOOPZ − 用於迴圈執行一組指令,直到滿足 ZF = 1 & CX = 0

LOOPNE/LOOPNZ − 用於迴圈執行一組指令,直到滿足 ZF = 0 & CX = 0

JCXZ − 如果 CX = 0,則跳轉到提供的地址

中斷指令

這些指令用於在程式執行期間呼叫中斷。

INT − 用於在執行過程中中斷程式並呼叫指定的程式。

INTO − 如果 OF = 1,則用於在執行過程中中斷程式

IRET − 用於從中斷服務返回主程式

微處理器 - 8086 中斷

中斷是一種在程式執行期間建立臨時暫停的方法,允許外圍裝置訪問微處理器。微處理器透過ISR(中斷服務例程)響應中斷,ISR 是一個簡短的程式,用於指示微處理器如何處理中斷。

下圖顯示了 8086 微處理器中的中斷型別:

硬體中斷

硬體中斷是由任何外圍裝置透過向微處理器傳送指定引腳的訊號引起的。

8086 具有兩個硬體中斷引腳,即 NMI 和 INTR。NMI 是不可遮蔽中斷,INTR 是可遮蔽中斷,優先順序較低。另一個相關的中斷引腳是 INTA,稱為中斷確認。

NMI

它是一個單一的不可遮蔽中斷引腳 (NMI),優先順序高於可遮蔽中斷請求引腳 (INTR),它是 2 型中斷。

當此中斷被啟用時,將發生以下操作:

完成當前正在執行的指令。

將標誌暫存器的值壓入堆疊。

將返回地址的 CS(程式碼段)值和 IP(指令指標)值壓入堆疊。

IP 從字地址 00008H 的內容載入。

CS 從下一個字地址 0000AH 的內容載入。

中斷標誌和陷阱標誌被重置為 0。

INTR

INTR 是可遮蔽中斷,因為只有在使用設定中斷標誌指令啟用中斷時,微處理器才會被中斷。不應使用清除中斷標誌指令啟用它。

INTR 中斷由 I/O 埠啟用。如果啟用了中斷並且停用了 NMI,則微處理器首先完成當前執行,並在 INTA 引腳上傳送兩次“0”。第一個“0”表示 INTA 通知外部裝置做好準備,在第二個“0”期間,微處理器從可程式設計中斷控制器接收 8 位資料,例如 X。

微處理器將採取以下操作:

首先完成當前指令。

啟用 INTA 輸出並接收中斷型別,例如 X。

將標誌暫存器值、返回地址的 CS 值和返回地址的 IP 值壓入堆疊。

IP 值從字地址 X × 4 的內容載入。

CS 從下一個字地址的內容載入。

中斷標誌和陷阱標誌被重置為 0

軟體中斷

在程式中的所需位置插入一些指令以建立中斷。這些中斷指令可用於測試各種中斷處理程式的工作情況。它包括:

INT- 帶型別號的中斷指令

這是一個 2 位元組指令。第一個位元組提供操作碼,第二個位元組提供中斷型別號。此組下有 256 種中斷型別。

其執行包括以下步驟:

將標誌暫存器值壓入堆疊。

將返回地址的 CS 值和返回地址的 IP 值壓入堆疊。

IP 從字地址“型別號”× 4 的內容載入。

CS 從下一個字地址的內容載入。

中斷標誌和陷阱標誌被重置為 0

0 型中斷的起始地址為 000000H,1 型中斷的起始地址為 00004H,2 型中斷的起始地址為 00008H,依此類推。前五個指標是專用中斷指標,即:

0 型中斷表示除零情況。

1 型中斷表示程式除錯期間的單步執行。

2 型中斷表示不可遮蔽 NMI 中斷。

3 型中斷表示斷點中斷。

4 型中斷表示溢位中斷。

5 型到 31 型中斷保留用於其他高階微處理器,32 型到 255 型中斷可用於硬體和軟體中斷。

INT 3-斷點中斷指令

這是一個 1 位元組指令,操作碼為 CCH。這些指令被插入到程式中,以便當處理器到達那裡時,它會停止程式的正常執行並遵循斷點過程。

其執行包括以下步驟:

將標誌暫存器值壓入堆疊。

將返回地址的 CS 值和返回地址的 IP 值壓入堆疊。

IP 從字地址 3×4 = 0000CH 的內容載入。

CS 從下一個字地址的內容載入。

中斷標誌和陷阱標誌被重置為 0

INTO- 溢位中斷指令

這是一個 1 位元組指令,其助記符為INTO。此指令的操作碼為 CEH。顧名思義,它是一個條件中斷指令,即只有當溢位標誌設定為 1 時才有效,並跳轉到中斷型別號為 4 的中斷處理程式。如果溢位標誌被複位,則執行繼續到下一條指令。

其執行包括以下步驟:

標誌暫存器值被壓入堆疊。

將返回地址的 CS 值和返回地址的 IP 值壓入堆疊。

IP 從字地址 4×4 = 00010H 的內容載入。

CS 從下一個字地址的內容載入。

中斷標誌和陷阱標誌被重置為 0

微處理器 - 8086 編址模式

在指令中表示源運算元的不同方法稱為編址模式。8086 程式設計中有 8 種不同的編址模式:

立即定址模式

資料運算元本身就是指令一部分的編址模式稱為立即定址模式。

示例

MOV CX, 4929 H, ADD AX, 2387 H, MOV AL, FFH

暫存器定址模式

這意味著暫存器是指令運算元的來源。

示例

MOV CX, AX ; copies the contents of the 16-bit AX register into

; the 16-bit CX register),

ADD BX, AX

直接定址模式

記憶體位置的有效地址直接寫在指令中的編址模式。

示例

MOV AX, [1592H], MOV AL, [0300H]

暫存器間接定址模式

此編址模式允許透過以下任何暫存器中儲存的偏移地址來定址任何記憶體位置的資料:BP、BX、DI 和 SI。

示例

MOV AX, [BX] ; Suppose the register BX contains 4895H, then the contents

; 4895H are moved to AX

ADD CX, {BX}

基址定址模式

在此編址模式下,運算元的偏移地址由 BX/BP 暫存器的內容和 8 位/16 位位移的總和給出。

示例

MOV DX, [BX+04], ADD CL, [BX+08]

索引定址模式

在此編址模式下,運算元的偏移地址透過將 SI 或 DI 暫存器的內容與 8 位/16 位位移相加來找到。

示例

MOV BX, [SI+16], ADD AL, [DI+16]

基址索引定址模式

在此編址模式下,運算元的偏移地址透過將基址暫存器的內容與索引暫存器的內容相加來計算。

示例

ADD CX, [AX+SI], MOV AX, [AX+DI]

帶位移的基址索引定址模式

在此編址模式下,運算元的偏移地址透過將基址暫存器的內容、索引暫存器的的內容和 8 位或 16 位位移相加來計算。

示例

MOV AX, [BX+DI+08], ADD CX, [BX+SI+16]

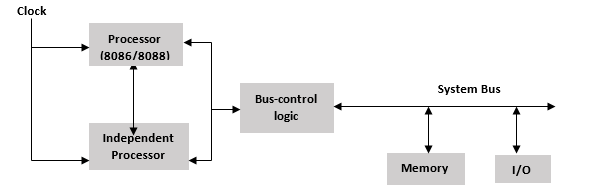

多處理器配置概述

多處理器是指同時執行指令的多組處理器。有三種基本的多處理器配置。

- 協處理器配置

- 緊密耦合配置

- 鬆散耦合配置

協處理器配置

協處理器是微處理器晶片上專門設計的電路,它可以非常快速地執行微處理器執行的相同任務。它減少了主處理器的負載。協處理器共享相同的記憶體、I/O 系統、匯流排、控制邏輯和時鐘發生器。協處理器處理諸如數學計算、螢幕圖形顯示等專業任務。

8086 和 8088 可以執行大部分操作,但它們的指令集無法執行復雜的數學運算,因此在這些情況下,微處理器需要數學協處理器,例如英特爾 8087 數學協處理器,它可以輕鬆快速地執行這些運算。

協處理器配置框圖

協處理器和處理器是如何連線的?

協處理器和處理器透過 TEST、RQ-/GT- 和 QS0 & QS1 訊號連線。

TEST 訊號連線到協處理器的 BUSY 引腳,其餘 3 個引腳連線到協處理器上相同名稱的 3 個引腳。

TEST 訊號負責協處理器的活動,即協處理器是繁忙還是空閒。

RT-/GT- 用於匯流排仲裁。

協處理器使用 QS0 & QS1 來跟蹤主機處理器的佇列狀態。

緊密耦合配置

緊密耦合配置類似於協處理器配置,即兩者共享相同的記憶體、I/O 系統匯流排、控制邏輯和控制發生器以及主機處理器。但是,協處理器和主機處理器獲取並執行自己的指令。系統匯流排由協處理器和主機處理器獨立控制。

緊密耦合配置框圖

處理器和獨立處理器是如何連線的?

主機和獨立處理器之間的通訊透過記憶體空間進行。

沒有指令用於通訊,例如 WAIT、ESC 等。

主機處理器管理記憶體,並透過向其一個埠傳送命令來喚醒獨立處理器。

然後,獨立處理器訪問記憶體以執行任務。

任務完成後,它使用狀態訊號或中斷請求向主機處理器傳送確認。

鬆散耦合配置

鬆散耦合配置由基於微處理器的系統模組組成,這些模組透過公共系統匯流排連線。每個模組都有自己的時鐘發生器、記憶體和 I/O 裝置,並透過本地匯流排連線。

鬆散耦合配置框圖

優點

擁有多個處理器可以提高效率。

每個處理器都有自己的本地匯流排來訪問本地記憶體/I/O 裝置。這使得實現並行處理變得容易。

系統結構靈活,即一個模組的故障不會影響整個系統的故障;有故障的模組可以稍後更換。

8087 數值資料處理器

8087 數字資料處理器也稱為數學協處理器、數字處理器擴充套件和浮點單元。它是英特爾設計的第一個數學協處理器,與 8086/8088 配合使用,從而使計算更容易、更快。

一旦 8086/8088 處理器識別出指令,它就會分配給 8087 協處理器進一步執行。

8087 支援的資料型別為:

- 二進位制整數

- 壓縮十進位制數

- 實數

- 臨時實數格式

8087 數字資料處理器的最突出特點如下:

它支援整數、浮點數和實數型別的資料,範圍從 2 到 10 個位元組。

處理速度非常快,它可以在 ~27 µs 內計算兩個 64 位實數的乘法,也可以在 ~35 µs 內計算平方根。

它遵循 IEEE 浮點標準。

8087 架構

8087 架構分為兩組,即控制單元 (CU) 和數字擴充套件單元 (NEU)。

控制單元處理處理器和記憶體之間的所有通訊,例如接收和解碼指令、讀取和寫入記憶體運算元、維護並行佇列等。所有協處理器指令都是 ESC 指令,即它們以“F”開頭,協處理器只執行 ESC 指令,而其他指令由微處理器執行。

數值擴充套件單元處理所有數值處理器指令,例如算術、邏輯、超越和資料傳輸指令。它具有8個暫存器堆疊,用於儲存指令的運算元及其結果。

8087協處理器的架構如下:

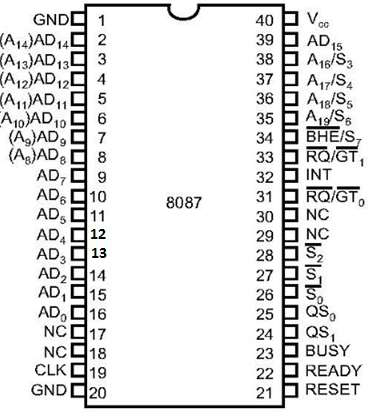

8087引腳描述

讓我們首先看一下8087的引腳圖:

以下列表提供了8087的引腳描述:

AD0 – AD15 − 這些是時間複用的地址/資料線,在第一個時鐘週期傳輸地址,從第二個時鐘週期開始傳輸資料。

A19 / S6 – A16/S − 這些線是時間複用的地址/狀態線。它的功能與8086的對應引腳類似。S6、S4和S3永久為高電平,而S5永久為低電平。

$\overline{BHE}$/S7 − 在第一個時鐘週期,$\overline{BHE}$/S7用於使能8086資料匯流排的高位元組資料,之後作為狀態線S7工作。

QS1, QS0 − 這些是佇列狀態輸入訊號,提供指令佇列的狀態,其狀態如以下表格所示:

| QS0 | QS1 | 狀態 |

|---|---|---|

| 0 | 0 | 無操作 |

| 0 | 1 | 佇列中操作碼的第一個位元組 |

| 1 | 0 | 清空佇列 |

| 1 | 1 | 佇列中的後續位元組 |

INT − 這是一箇中斷訊號,當執行過程中接收到未遮蔽的異常時,它變為高電平。

BUSY − 這是一個輸出訊號,當它為高電平時表示協處理器處於繁忙狀態。

READY − 這是一個輸入訊號,用於通知協處理器匯流排是否準備好接收資料。

RESET − 這是一個輸入訊號,用於重置協處理器的內部活動,並在CPU需要時準備進行進一步執行。

CLK − CLK輸入提供處理器操作的基本時序。

VCC − 這是一個電源訊號,電路工作需要+5V電源。

S0, S1, S2 − 這些是狀態訊號,提供操作的狀態,8087匯流排控制器使用這些訊號生成記憶體和I/O控制訊號。這些訊號在第四個時鐘週期有效。

| S2 | S1 | S0 | 佇列狀態 |

|---|---|---|---|

| 0 | X | X | 未使用 |

| 1 | 0 | 0 | 未使用 |

| 1 | 0 | 1 | 記憶體讀 |

| 1 | 1 | 0 | 記憶體寫 |

| 1 | 1 | 1 | 被動 |

RQ/GT1 & RQ/GT0 − 這些是請求/授權訊號,8087處理器使用這些訊號從主機處理器8086/8088獲取匯流排控制權以進行運算元傳輸。

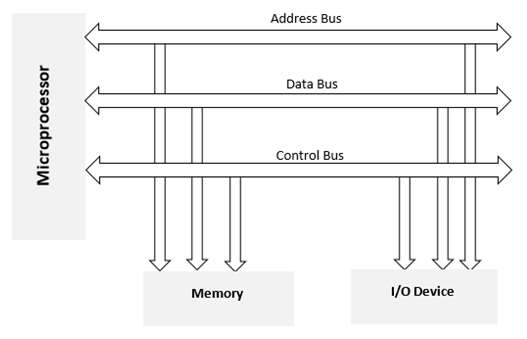

微處理器 - I/O介面概述

本章將討論8085的記憶體介面和I/O介面。

介面是兩個元件之間通訊的路徑。介面分為兩種型別:記憶體介面和I/O介面。

記憶體介面

執行任何指令時,都需要微處理器訪問記憶體以讀取指令程式碼和儲存在記憶體中的資料。為此,記憶體和微處理器都需要一些訊號來讀取和寫入暫存器。

介面過程包括一些關鍵因素,以匹配記憶體需求和微處理器訊號。因此,介面電路的設計應使其能夠將記憶體訊號需求與微處理器的訊號匹配。

IO介面

有各種通訊裝置,例如鍵盤、滑鼠、印表機等。因此,我們需要使用鎖存器和緩衝器將鍵盤和其他裝置與微處理器介面。這種型別的介面稱為I/O介面。

記憶體和I/O介面的框圖

8085介面引腳

以下是用於與其他裝置介面的8085引腳列表:

- A15 - A8(高地址匯流排)

- AD7 - AD0(低地址/資料匯流排)

- ALE

- RD

- WR

- READY

通訊方式 - 微處理器與外部世界?

微處理器連線外部世界有兩種通訊方式。

- 序列通訊介面

- 並行通訊介面

序列通訊介面 - 在這種型別的通訊中,介面從微處理器獲取單個位元組的資料,並逐位地將其序列傳送到另一個系統,反之亦然。

並行通訊介面 - 在這種型別的通訊中,介面從微處理器獲取一個位元組的資料,並將其同時(或)並行地逐位傳送到其他系統,反之亦然。

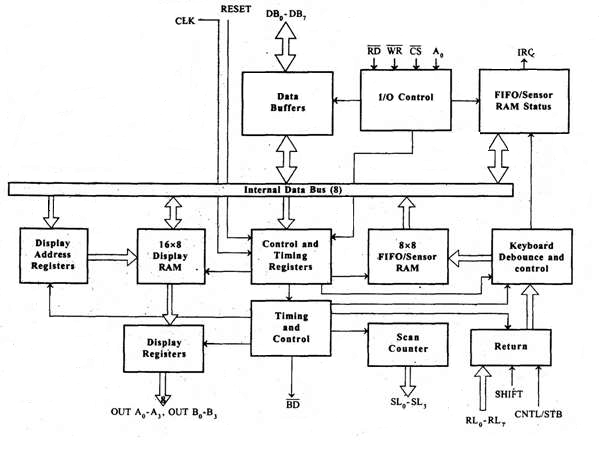

8279 - 可程式設計鍵盤

8279可程式設計鍵盤/顯示控制器由英特爾設計,用於將鍵盤與CPU介面。鍵盤首先掃描鍵盤並識別是否有任何鍵被按下。然後,它將被按下鍵的相對響應傳送到CPU,反之亦然。

鍵盤與CPU介面有多少種方式?

鍵盤可以透過中斷模式或輪詢模式與CPU介面。在中斷模式下,只有在按下任何鍵時才請求處理器服務,否則CPU將繼續其主要任務。

在輪詢模式下,CPU定期讀取8279的內部標誌,以檢查是否有鍵被按下。

8279鍵盤如何工作?

鍵盤最多包含64個鍵,它們使用鍵碼與CPU介面。這些鍵碼經過去抖動處理並存儲在8位元組FIFO RAM中,CPU可以訪問該RAM。如果在FIFO中輸入超過8個字元,則意味著一次按下了8個以上的鍵。這時會設定溢位狀態。

如果FIFO包含有效的鍵輸入,則在中斷模式下中斷CPU,否則CPU在輪詢中檢查狀態以讀取輸入。一旦CPU讀取鍵輸入,FIFO就會更新,鍵輸入就會從FIFO中彈出以騰出空間以供新的輸入。

架構和描述

I/O控制和資料緩衝區

該單元控制資料在微處理器中的流動。只有當D為低電平時才啟用它。它的資料緩衝區將系統的外部匯流排與微處理器的內部匯流排介面。A0、RD和WR引腳用於命令、狀態或資料讀/寫操作。

控制和定時暫存器以及定時控制

該單元包含暫存器,用於儲存鍵盤、顯示模式以及CPU程式設計的其他操作。定時和控制單元處理電路操作的定時。

掃描計數器

它有兩種模式,即編碼模式和解碼模式。在編碼模式下,計數器提供二進位制計數,該計數將被外部解碼以提供鍵盤和顯示器的掃描線。

在解碼掃描模式下,計數器內部解碼最低兩位,並在SL0-SL3上提供解碼的1選4掃描。

返回緩衝區、鍵盤去抖和控制

該單元首先逐行掃描鍵閉合,如果找到,則鍵盤去抖單元對鍵輸入進行去抖動處理。如果檢測到相同的鍵,則該鍵的程式碼將與SHIFT和CONTROL鍵狀態一起直接傳輸到感測器RAM。

FIFO/感測器RAM和狀態邏輯

該單元充當8位元組先進先出(FIFO) RAM,每個被按下鍵的鍵碼都按其順序輸入到RAM中。狀態邏輯在每次FIFO讀取操作後生成中斷請求,直到FIFO為空。

在掃描感測器矩陣模式下,該單元充當感測器RAM,其每一行都載入了感測器矩陣中相應行的狀態。當感測器改變其狀態時,IRQ線變為高電平並中斷CPU。

顯示地址暫存器和顯示RAM

該單元包含顯示地址暫存器,該暫存器儲存CPU當前從顯示RAM讀/寫的資料的地址。

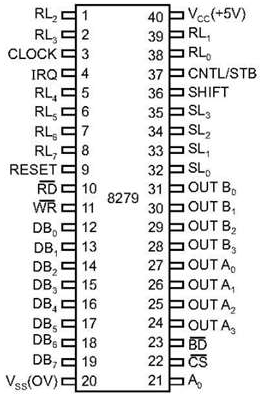

8279 - 引腳描述

下圖顯示了8279的引腳圖:

資料匯流排線,DB0 - DB7

這是8條雙向資料匯流排,用於與CPU之間傳輸資料。

CLK

時鐘輸入用於生成微處理器所需的內部時序。

復位

顧名思義,此引腳用於復位微處理器。

CS片選

當此引腳設定為低電平時,允許讀/寫操作,否則此引腳應設定為高電平。

A0

此引腳指示命令/狀態資訊的傳輸。當它為低電平時,表示資料傳輸。

RD, WR

此讀/寫引腳使資料緩衝區能夠透過資料匯流排傳送/接收資料。

IRQ

當FIFO感測器RAM中有資料時,此中斷輸出線變為高電平。每進行一次FIFO RAM讀取操作,中斷線都變為低電平。但是,如果FIFO RAM中還有任何鍵碼輸入需要CPU讀取,則此引腳再次變為高電平,從而向CPU生成中斷。

Vss, Vcc

這些是微處理器的接地和電源線。

SL0 − SL3

這些是掃描線,用於掃描鍵盤矩陣和顯示數字。可以使用模式控制暫存器將這些線程式設計為編碼或解碼。

RL0 − RL7

這些是返回線,連線到鍵的一個端子,而鍵的另一個端子連線到解碼的掃描線。當按下任何鍵時,這些線設定為0。

SHIFT

在掃描鍵盤模式下,Shift輸入線狀態與FIFO中的每個鍵碼一起儲存。在用鍵閉合將其下拉之前,它會在內部上拉以保持高電平。

CNTL/STB - 控制/選通輸入模式

在鍵盤模式下,此線用作控制輸入,並在鍵閉合時儲存在FIFO中。在選通輸入模式下,該線是一個選通線,將資料輸入FIFO RAM。它具有內部上拉電阻。該線透過鍵閉合下拉。

BD

它代表空白顯示。它用於在數字切換期間使顯示變為空白。

OUTA0 – OUTA3 和 OUTB0 – OUTB3

這些是用於兩個16x4或一個16x8內部顯示重新整理暫存器的輸出埠。來自這些線的資料與掃描線同步,以掃描顯示器和鍵盤。

8279的操作模式

8279有兩種操作模式:輸入模式和輸出模式。

輸入模式

此模式處理鍵盤給出的輸入,此模式進一步分為3種模式。

掃描鍵盤模式 - 在此模式下,可以使用編碼掃描或解碼掃描來介面鍵矩陣。在編碼掃描中,可以介面8×8鍵盤;在解碼掃描中,可以介面4×8鍵盤。帶有SHIFT和CONTROL狀態的被按下鍵的程式碼儲存到FIFO RAM中。

掃描感測器矩陣 - 在此模式下,可以使用編碼器掃描或解碼器掃描將感測器陣列與處理器介面。在編碼器掃描中,可以介面8×8感測器矩陣;在解碼器掃描中,可以介面4×8感測器矩陣。

選通輸入 - 在此模式下,當控制線設定為0時,返回線上的資料將逐位元組儲存在FIFO中。

輸出模式

此模式處理與顯示相關的操作。此模式進一步分為兩種輸出模式。

顯示掃描 - 此模式允許將8/16個字元多路複用顯示器組織為雙4位/單8位顯示單元。

顯示輸入 - 此模式允許從右側/左側輸入要顯示的資料。

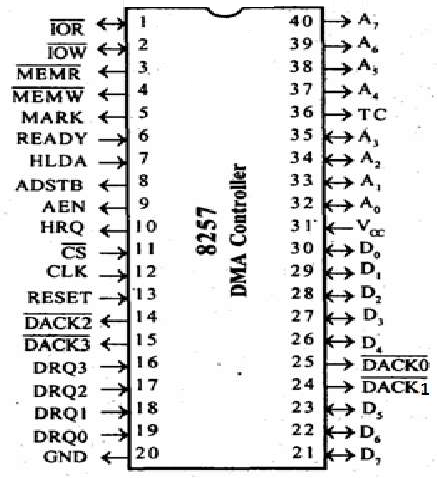

微處理器 - 8257 DMA控制器

DMA 指的是直接記憶體訪問 (Direct Memory Access)。它是英特爾設計的,用於以最快速度傳輸資料。它允許裝置直接與記憶體之間傳輸資料,而無需 CPU 干預。

使用 DMA 控制器,裝置請求 CPU 保持其資料、地址和控制匯流排,以便裝置可以自由地直接與記憶體之間傳輸資料。只有在收到 CPU 的 HLDA 訊號後,才會啟動 DMA 資料傳輸。

DMA 操作是如何執行的?

以下是 DMA 執行的操作序列:

最初,當任何裝置必須在裝置和記憶體之間傳送資料時,裝置必須向 DMA 控制器傳送 DMA 請求 (DRQ)。

DMA 控制器向 CPU 傳送保持請求 (HRQ),並等待 CPU 確認 HLDA。

然後,微處理器將所有資料匯流排、地址匯流排和控制匯流排置為高阻態。CPU 放棄對匯流排的控制,並透過 HLDA 訊號確認 HOLD 請求。

現在 CPU 處於 HOLD 狀態,DMA 控制器必須管理 CPU、記憶體和 I/O 裝置之間總線上的操作。

8257 的特點

以下是 8257 的一些主要特點:

它有四個通道,可用於四個 I/O 裝置。

每個通道具有 16 位地址和 14 位計數器。

每個通道最多可以傳輸 64kb 的資料。

每個通道可以獨立程式設計。

每個通道可以執行讀取傳輸、寫入傳輸和驗證傳輸操作。

它向外圍裝置生成 MARK 訊號,表示已傳輸 128 位元組。

它需要一個單相時鐘。

其頻率範圍為 250Hz 至 3MHz。

它以兩種模式執行,即 **主模式** 和 **從模式**。

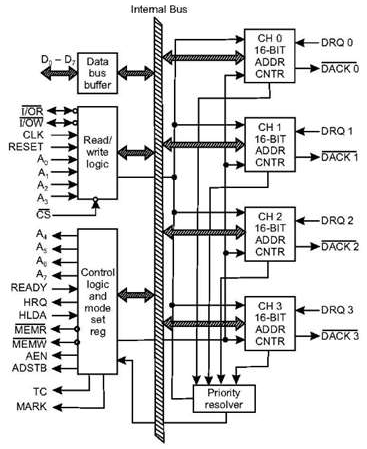

8257 架構

下圖顯示了 8257 的架構:

8257 引腳描述

下圖顯示了 8257 DMA 控制器的引腳圖:

DRQ0−DRQ3

這些是四個獨立的通道 DMA 請求輸入,外圍裝置使用它們來使用 DMA 服務。當選擇固定優先順序模式時,DRQ0 具有最高的優先順序,而 DRQ3 具有最低的優先順序。

DACKo − DACK3

這些是低電平有效的 DMA 確認線,它們透過 CPU 向請求外圍裝置更新其請求的狀態。這些線也可以作為請求裝置的選通線。

Do − D7

這些是雙向資料線,用於將系統匯流排與 DMA 控制器的內部資料匯流排連線。在從模式下,它將命令字傳輸到 8257,並將狀態字從 8257 傳輸出來。在主模式下,這些線用於將生成的地址的高位位元組傳送到鎖存器。此地址將進一步使用 ADSTB 訊號鎖存。

IOR

它是一個低電平有效的雙向三態輸入線,CPU 在從模式下使用它來讀取 8257 的內部暫存器。在主模式下,它用於在記憶體寫入週期期間從外圍裝置讀取資料。

IOW

它是一個低電平有效的雙向三態線,用於將資料匯流排的內容載入到 8 位模式暫存器或 16 位 DMA 地址暫存器或終端計數暫存器的高/低位位元組。在主模式下,它用於在 DMA 記憶體讀取週期期間將資料載入到外圍裝置。

CLK

這是 8257 內部操作所需的時鐘頻率訊號。

復位

此訊號用於透過停用所有 DMA 通道來重置 DMA 控制器。

Ao - A3

這些是四個最低有效地址線。在從模式下,它們充當輸入,用於選擇要讀取或寫入的暫存器之一。在主模式下,它們是 8257 生成的四個最低有效記憶體地址輸出線。

CS

它是一個低電平有效的片選線。在從模式下,它啟用對 8257 的讀/寫操作。在主模式下,它停用對 8257 的讀/寫操作。

A4 - A7

這些是 DMA 在主模式下生成的下位元組地址的高四位。

READY

它是一個高電平有效的非同步輸入訊號,透過插入等待狀態使 DMA 就緒。

HRQ

此訊號用於接收來自輸出裝置的保持請求訊號。在從模式下,它與 8257 的 DRQ 輸入線連線。在主模式下,它與 CPU 的 HOLD 輸入連線。

HLDA

這是保持確認訊號,當它設定為 1 時,表示 DMA 控制器 CPU 已將匯流排授予請求外圍裝置。

MEMR

它是低電平有效的記憶體讀取訊號,用於在 DMA 讀取週期期間從定址的記憶體位置讀取資料。

MEMW

它是低電平有效的三態訊號,用於在 DMA 寫入操作期間將資料寫入定址的記憶體位置。

ADST

此訊號用於將 DMA 控制器生成的記憶體地址的高位位元組轉換為鎖存器。

AEN

此訊號用於停用地址匯流排/資料匯流排。

TC

它代表“終端計數”,它向當前外圍裝置指示當前 DMA 週期。

MARK

從開始起每 128 個週期或其整數倍數啟用標記。它表示當前 DMA 週期是自上次向所選外圍裝置輸出 MARK 訊號以來的第 128 個週期。

Vcc

它是電路操作所需的電源訊號。

微控制器 - 概述

**微控制器**是一種小型且低成本的微型計算機,旨在執行嵌入式系統的特定任務,例如顯示微波爐的資訊、接收遠端訊號等。

一般的微控制器包括處理器、記憶體(RAM、ROM、EPROM)、序列埠、外圍裝置(定時器、計數器)等。

微處理器和微控制器的區別

下表重點介紹了微處理器和微控制器之間的區別:

| 微控制器 | 微處理器 |

|---|---|

| 微控制器用於在一個應用程式中執行單個任務。 | 微處理器用於大型應用程式。 |

| 其設計和硬體成本低。 | 其設計和硬體成本高。 |

| 易於更換。 | 不容易更換。 |

| 它採用 CMOS 技術製造,執行功耗低。 | 其功耗高,因為它必須控制整個系統。 |

| 它由 CPU、RAM、ROM、I/O 埠組成。 | 它不包含 RAM、ROM、I/O 埠。它使用其引腳與外圍裝置介面。 |

微控制器的型別

根據記憶體、架構、位和指令集,微控制器分為不同的類別。以下是它們的型別列表:

位

基於位配置,微控制器進一步分為三類。

**8 位微控制器** - 此型別的微控制器用於執行算術和邏輯運算,例如加法、減法、乘法、除法等。例如,Intel 8031 和 8051 是 8 位微控制器。

**16 位微控制器** - 此型別的微控制器用於執行需要更高精度和效能的算術和邏輯運算。例如,Intel 8096 是一款 16 位微控制器。

**32 位微控制器** - 此型別的微控制器通常用於自動控制裝置,例如自動操作機器、醫療裝置等。

記憶體

基於記憶體配置,微控制器進一步分為兩類。

**外部記憶體微控制器** - 此型別的微控制器設計為晶片上沒有程式記憶體。因此,它被稱為外部記憶體微控制器。例如:Intel 8031 微控制器。

**嵌入式記憶體微控制器** - 此型別的微控制器設計為微控制器的所有程式和資料記憶體、計數器和定時器、中斷、I/O 埠都嵌入在晶片上。例如:Intel 8051 微控制器。

指令集

基於指令集配置,微控制器進一步分為兩類。

**CISC** - CISC 代表複雜指令集計算機。它允許使用者插入單個指令作為許多簡單指令的替代方案。

**RISC** - RISC 代表精簡指令集計算機。它透過縮短每個指令的時鐘週期來減少操作時間。

微控制器的應用

微控制器廣泛應用於各種不同的裝置,例如:

光線感測和控制裝置,如 LED。

溫度感測和控制裝置,如微波爐、煙囪。

火災探測和安全裝置,如火災報警器。

測量裝置,如電壓表。

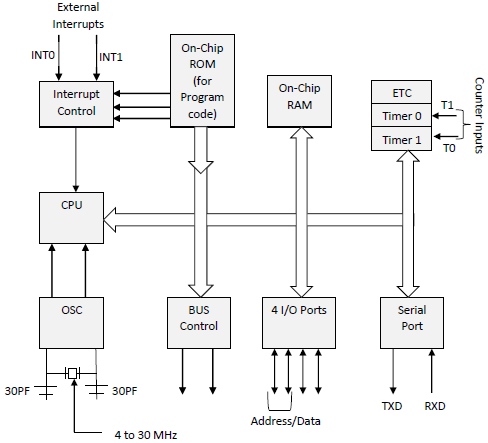

微控制器 - 8051 架構

8051 微控制器由英特爾於 1981 年設計。它是一款 8 位微控制器。它採用 40 引腳 DIP(雙列直插式封裝)製造,具有 4kb 的 ROM 儲存空間和 128 位元組的 RAM 儲存空間,以及 2 個 16 位定時器。它包含四個並行的 8 位埠,這些埠是可程式設計的,也可以根據需要定址。片上晶體振盪器整合在微控制器中,晶體頻率為 12 MHz。

現在讓我們討論 8051 微控制器的架構。

在下圖中,系統匯流排將所有支援裝置連線到 CPU。系統匯流排由 8 位資料匯流排、16 位地址匯流排和匯流排控制訊號組成。所有其他裝置,如程式記憶體、埠、資料記憶體、序列介面、中斷控制、定時器和 CPU,都透過系統匯流排相互連線。

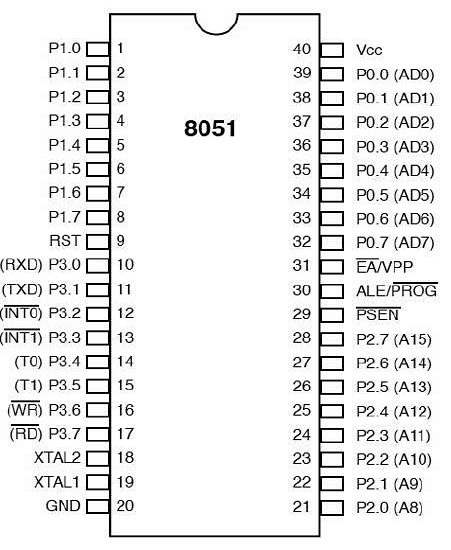

微控制器 - 8051 引腳描述

8051 微控制器的引腳圖如下所示:

**引腳 1 至 8** - 這些引腳稱為埠 1。此埠不執行任何其他功能。它是內部上拉的雙向 I/O 埠。

**引腳 9** - 它是一個復位引腳,用於將微控制器復位到其初始值。

**引腳 10 至 17** - 這些引腳稱為埠 3。此埠執行一些功能,例如中斷、定時器輸入、控制訊號、序列通訊訊號 RxD 和 TxD 等。

**引腳 18 和 19** - 這些引腳用於連線外部晶體以獲得系統時鐘。

**引腳 20** - 此引腳為電路提供電源。

**引腳 21 至 28** - 這些引腳稱為埠 2。它用作 I/O 埠。高位地址匯流排訊號也使用此埠進行多路複用。

**引腳 29** - 這是 PSEN 引腳,代表程式儲存器啟用。它用於從外部程式儲存器讀取訊號。

**引腳 30** - 這是 EA 引腳,代表外部訪問輸入。它用於啟用/停用外部記憶體介面。

**引腳 31** - 這是 ALE 引腳,代表地址鎖存器啟用。它用於解複用埠的地址-資料訊號。

**引腳 32 至 39** - 這些引腳稱為埠 0。它用作 I/O 埠。低位地址和資料匯流排訊號使用此埠進行多路複用。

**引腳 40** - 此引腳用於為電路提供電源。

微控制器 8051 輸入輸出埠

8051 微控制器有 4 個 8 位 I/O 埠,可以配置為輸入或輸出。因此,總共 32 個輸入/輸出引腳允許微控制器與外圍裝置連線。

**引腳配置**,即引腳可以根據邏輯狀態配置為 1(輸入)和 0(輸出)。

輸入/輸出 (I/O) 引腳 − 微控制器內部的所有電路都必須連線到它的一個引腳,P0埠除外,因為它沒有內建上拉電阻。

輸入引腳 − 將邏輯1應用於P暫存器的一個位。輸出FE電晶體關閉,另一個引腳透過高阻上拉電阻保持連線到電源電壓。

P0埠 − P0(零)埠具有兩個功能:

當使用外部儲存器時,低地址位元組(地址A0A7)應用於它;否則,此埠的所有位都配置為輸入/輸出。

當P0埠配置為輸出時,其他埠包含帶有內建上拉電阻的引腳(其一端連線到5V電源),而此埠的引腳則缺少該電阻。

輸入配置

如果此埠的任何引腳配置為輸入,則其行為就像“浮動”一樣,即輸入具有無限的輸入電阻和不確定的電位。

輸出配置

當引腳配置為輸出時,它充當“開漏”輸出。透過將邏輯0應用於埠位,相應的引腳將連線到地 (0V);應用邏輯1時,外部輸出將保持“浮動”。

為了在此輸出引腳上應用邏輯1 (5V),需要構建一個外部上拉電阻。

P1埠

P1是一個真正的I/O埠,因為它不像P0那樣具有任何替代功能,但此埠只能配置為通用I/O。它具有內建上拉電阻,並完全相容TTL電路。

P2埠

當使用外部儲存器時,P2類似於P0。此埠的引腳佔據了為外部儲存器晶片設計的地址。此埠可用於具有地址A8-A15的較高地址位元組。如果沒有新增儲存器,則此埠可用作類似於P1埠的通用輸入/輸出埠。

P3埠

在此埠中,功能與其他埠類似,只是必須將邏輯1應用於P3暫存器的相應位。

引腳電流限制

當引腳配置為輸出(即邏輯0)時,單個埠引腳可以接收10mA的電流。

當這些引腳配置為輸入(即邏輯1)時,內建上拉電阻提供非常微弱的電流,但可以啟用多達4個LS系列TTL輸入。

如果埠的所有8位都處於活動狀態,則總電流必須限制在15mA(P0埠:26mA)。

如果所有埠(32位)都處於活動狀態,則總最大電流必須限制在71mA。

微控制器 - 8051 中斷

中斷是暫時掛起主程式、將控制權傳遞給外部源並執行其任務的事件。然後,它將控制權傳遞迴主程式中斷停止的地方。

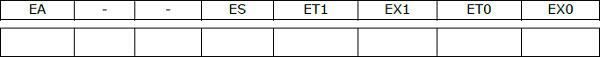

8051有5箇中斷訊號,即INT0、TF0、INT1、TF1、RI/TI。可以透過設定IE暫存器的位來啟用或停用每個中斷,並且可以透過清除同一暫存器的EA位來停用整個中斷系統。

IE(中斷允許)暫存器

此暫存器負責啟用和停用中斷。將EA暫存器設定為1以啟用中斷,設定為0以停用中斷。其位序列及其含義如下圖所示。

| EA | IE.7 | 它停用所有中斷。當EA = 0時,不會確認任何中斷;EA = 1則分別啟用中斷。 |

| - | IE.6 | 保留供將來使用。 |

| - | IE.5 | 保留供將來使用。 |

| ES | IE.4 | 啟用/停用序列埠中斷。 |

| ET1 | IE.3 | 啟用/停用定時器1溢位中斷。 |

| EX1 | IE.2 | 啟用/停用外部中斷1。 |

| ET0 | IE.1 | 啟用/停用定時器0溢位中斷。 |

| EX0 | IE.0 | 啟用/停用外部中斷0。 |

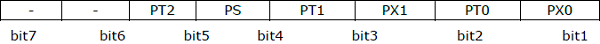

IP(中斷優先順序)暫存器

我們可以透過更改中斷優先順序 (IP) 暫存器中相應的位來更改中斷的優先順序級別,如下圖所示。

低優先順序中斷只能被高優先順序中斷中斷,但不能被另一個低優先順序中斷中斷。

如果同時收到不同優先順序的兩個中斷請求,則優先處理高優先順序請求。

如果同時收到相同優先順序的請求,則內部輪詢順序決定要處理哪個請求。

| - | IP.6 | 保留供將來使用。 |

| - | IP.5 | 保留供將來使用。 |

| PS | IP.4 | 它定義序列埠中斷的優先順序。 |

| PT1 | IP.3 | 它定義定時器1中斷的優先順序。 |

| PX1 | IP.2 | 它定義外部中斷1的優先順序。 |

| PT0 | IP.1 | 它定義定時器0中斷的優先順序。 |

| PX0 | IP.0 | 它定義外部中斷0的優先順序。 |

TCON暫存器

TCON暫存器指定微控制器外部中斷的型別。

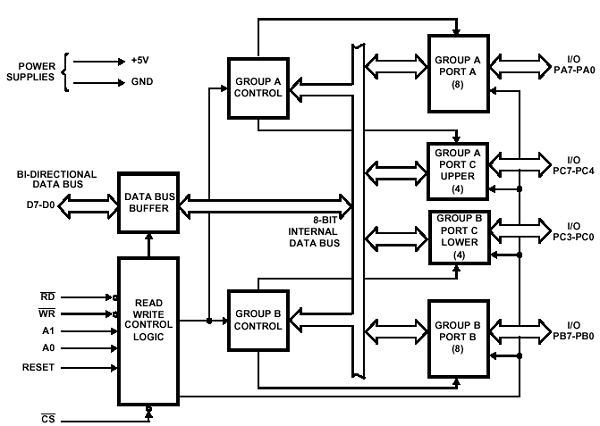

8255A - 可程式設計外設介面

8255A是一種通用的可程式設計I/O裝置,旨在根據需要在特定條件下將資料從I/O傳輸到中斷I/O。它幾乎可以與任何微處理器一起使用。

它包含三個8位雙向I/O埠(24條I/O線),可以根據需要進行配置。

8255A的埠

8255A有三個埠:埠A、埠B和埠C。

埠A包含一個8位輸出鎖存器/緩衝器和一個8位輸入緩衝器。

埠B類似於埠A。

埠C可以透過控制字分為兩部分:埠C下半部分 (PC0-PC3) 和埠C上半部分 (PC7-PC4)。

這三個埠進一步分為兩組:A組包括埠A和埠C上半部分;B組包括埠B和埠C下半部分。這兩組可以用三種不同的模式進行程式設計:第一種模式稱為模式0,第二種模式稱為模式1,第三種模式稱為模式2。

工作模式

8255A有三種不同的工作模式:

模式0 − 在此模式下,埠A和B用作兩個8位埠,埠C用作兩個4位埠。每個埠都可以程式設計為輸入模式或輸出模式,其中輸出是鎖存的,而輸入不是鎖存的。埠不具有中斷能力。

模式1 − 在此模式下,埠A和B用作8位I/O埠。它們可以配置為輸入埠或輸出埠。每個埠使用埠C中的三條線作為握手訊號。輸入和輸出是鎖存的。

模式2 − 在此模式下,埠A可以配置為雙向埠,埠B可以配置為模式0或模式1。埠A使用埠C中的五個訊號作為資料傳輸的握手訊號。埠C的其餘三個訊號可以用作簡單的I/O或埠B的握手訊號。

8255A的功能

8255A的主要功能如下:

它包含3個8位IO埠,即PA、PB和PC。

地址/資料匯流排必須在外部進行多路分解。

它與TTL相容。

它具有改進的直流驅動能力。

8255架構

下圖顯示了8255A的架構:

Intel 8255A - 引腳描述

讓我們首先看一下Intel 8255A的引腳圖:

現在讓我們討論8255A中引腳的功能描述。

資料匯流排緩衝器

這是一個三態8位緩衝器,用於將微處理器與系統資料匯流排連線。資料根據CPU的指令由緩衝器傳輸或接收。控制字和狀態資訊也透過此匯流排傳輸。

讀/寫控制邏輯

此塊負責控制資料/控制/狀態字的內部/外部傳輸。它接收來自CPU地址和控制匯流排的輸入,然後向兩個控制組發出命令。

CS

它代表片選。此輸入的低電平選擇晶片並啟用8255A和CPU之間的通訊。它連線到解碼地址,A0 & A1連線到微處理器地址線。

其結果取決於以下條件:

| CS | A1 | A0 | 結果 |

|---|---|---|---|

| 0 | 0 | 0 | 埠A |

| 0 | 0 | 1 | 埠B |

| 0 | 1 | 0 | 埠C |

| 0 | 1 | 1 | 控制暫存器 |

| 1 | X | X | 無選擇 |

WR

它代表寫操作。此控制訊號啟用寫操作。當此訊號變低時,微處理器寫入選定的I/O埠或控制暫存器。

復位

這是一個高電平有效訊號。它清除控制暫存器並將所有埠設定為輸入模式。

RD

它代表讀操作。此控制訊號啟用讀操作。當訊號為低電平時,微處理器從8255的選定I/O埠讀取資料。

A0和A1

這些輸入訊號與RD、WR和一個控制訊號一起工作。下表顯示了它們的各種訊號及其結果。

| A1 | A0 | RD | WR | CS | 結果 |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 輸入操作 埠A → 資料匯流排 |

| 0 | 1 | 0 | 1 | 0 | 埠B → 資料匯流排 |

| 1 | 0 | 0 | 1 | 0 | 埠C → 資料匯流排 |

| 0 | 0 | 1 | 0 | 0 | 輸出操作 資料匯流排 → 埠A |

| 0 | 1 | 1 | 0 | 0 | 資料匯流排 → 埠A |

| 1 | 0 | 1 | 0 | 0 | 資料匯流排 → 埠B |

| 1 | 1 | 1 | 0 | 0 | 資料匯流排 → 埠D |

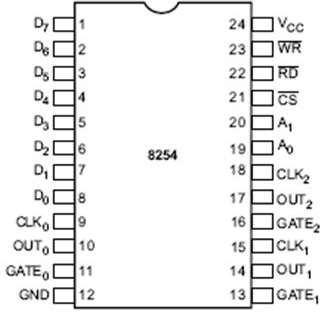

Intel 8253 - 可程式設計定時器

Intel 8253和8254是可程式設計定時器 (PTI),設計用於微處理器使用三個16位暫存器執行計時和計數功能。每個計數器有兩個輸入引腳,即時鐘和門,還有一個“OUT”輸出引腳。要操作計數器,需要在其暫存器中載入一個16位計數。根據命令,它開始遞減計數,直到達到0,然後它產生一個脈衝,該脈衝可用於中斷CPU。

8253和8254的區別

下表區分了8253和8254的功能:

| 8253 | 8254 |

|---|---|

| 其工作頻率為0 - 2.6 MHz | 其工作頻率為0 - 10 MHz |

| 它使用N-MOS技術 | 它使用H-MOS技術 |

| 回讀命令不可用 | 回讀命令可用 |

| 同一計數器的讀寫不能交錯。 | 同一計數器的讀寫可以交錯。 |

8253/54的功能

8253/54最突出的功能如下:

它具有三個獨立的16位向下計數器。

它可以處理從DC到10 MHz的輸入。

這三個計數器可以程式設計為二進位制或BCD計數。

它幾乎與所有微處理器相容。

8254有一個強大的命令,稱為回讀命令,允許使用者檢查計數值、程式設計模式、當前模式和計數器的當前狀態。

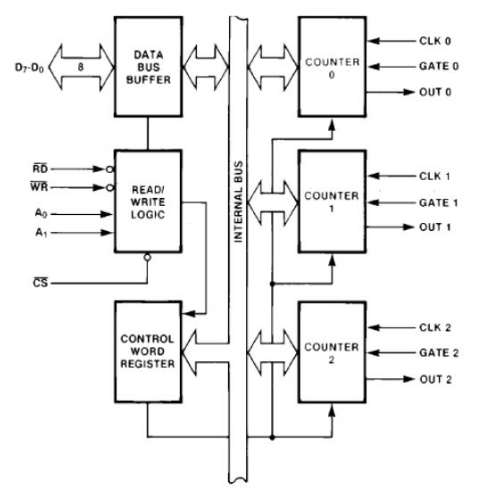

8254架構

8254的架構如下所示:

8254引腳說明

以下是8254的引腳圖:

在上圖中,有三個計數器、一個數據匯流排緩衝器、讀/寫控制邏輯和一個控制暫存器。每個計數器有兩個輸入訊號 - 時鐘和門,以及一個輸出訊號 - OUT。

資料匯流排緩衝器

這是一個三態、雙向、8位緩衝器,用於將8253/54介面到系統資料匯流排。它具有三個基本功能:

- 程式設計8253/54的模式。

- 載入計數暫存器。

- 讀取計數值。

讀/寫邏輯

它包括5個訊號,即RD、WR、CS和地址線A0 & A1。在外設I/O模式下,RD和WR訊號分別連線到IOR和IOW。在記憶體對映I/O模式下,它們連線到MEMR和MEMW。

CPU的地址線A0 & A1連線到8253/54的A0和A1線,CS連線到解碼地址。控制字暫存器和計數器根據A0 & A1線上的訊號進行選擇。

| A1 | A0 | 結果 |

|---|---|---|

| 0 | 0 | 計數器0 |

| 0 | 1 | 計數器1 |

| 1 | 0 | 計數器2 |

| 1 | 1 | 控制字暫存器 |

| X | X | 無選擇 |

控制字暫存器

當A0 & A1線為邏輯1時訪問該暫存器。它用於寫入命令字,該命令字指定要使用的計數器、其模式以及讀或寫操作。下表顯示了各種控制輸入的結果。

| A1 | A0 | RD | WR | CS | 結果 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 寫入計數器0 |

| 0 | 1 | 1 | 0 | 0 | 寫入計數器1 |

| 1 | 0 | 1 | 0 | 0 | 寫入計數器2 |

| 1 | 1 | 1 | 0 | 0 | 寫入控制字 |

| 0 | 0 | 0 | 1 | 0 | 讀取計數器0 |

| 0 | 1 | 0 | 1 | 0 | 讀取計數器1 |

| 1 | 0 | 0 | 1 | 0 | 讀取計數器2 |

| 1 | 1 | 0 | 1 | 0 | 無操作 |

| X | X | 1 | 1 | 0 | 無操作 |

| X | X | X | X | 1 | 無操作 |

計數器

每個計數器由一個16位單向下計數器組成,它可以以二進位制或BCD方式工作。其輸入和輸出由控制字暫存器中儲存的模式選擇配置。程式設計師可以讀取任何三個計數器的內容,而不會干擾正在進行的實際計數。

Intel 8253/54 - 工作模式

8253/54可以以6種不同的模式工作。本章將討論這些工作模式。

模式0 ─ 終端計數中斷

它用於在一定時間間隔後向微處理器產生中斷。

模式設定後,輸出最初為低電平。將計數值載入到計數器後,輸出保持低電平。

計數器遞減的過程持續到達到終端計數,即計數變為零,輸出變為高電平,並將保持高電平,直到重新載入新的計數。

GATE訊號為高電平時進行正常計數。當GATE變為低電平時,計數終止,當前計數被鎖存,直到GATE再次變為高電平。

模式1 – 可程式設計單穩態

它可以用作單穩態多諧振盪器。

門輸入在此模式下用作觸發輸入。

輸出保持高電平,直到載入計數並應用觸發訊號。

模式2 – 頻率發生器

初始化後,輸出通常為高電平。

每當計數變為零時,輸出端就會產生另一個低脈衝,計數器將被重新載入。

模式3 – 方波發生器

此模式類似於模式2,只是輸出在計時器週期的一半時間內保持低電平,在另一半時間內保持高電平。

模式4 − 軟體觸發模式

在此模式下,輸出將保持高電平,直到計時器計數到零,此時輸出將脈衝低電平然後再次變為高電平。

當GATE訊號變為低電平時,計數被鎖存。

在終端計數時,輸出變為低電平一個時鐘週期,然後變為高電平。此低脈衝可以用作脈衝訊號。

模式5 – 硬體觸發模式

此模式響應外部生成的訊號產生脈衝訊號。

此模式類似於模式4,只是計數是由門輸入處的訊號啟動的,這意味著它是硬體觸發的,而不是軟體觸發的。

初始化後,輸出變為高電平。

達到終端計數時,輸出變為低電平一個時鐘週期。