- 8085 微處理器

- 微處理器 - 8085 架構

- 8085 引腳配置

- 定址方式和中斷

- 8085 指令集

- 多處理器配置

- 配置概述

- 8087 數值資料處理器

- I/O 介面

- I/O 介面概述

- 8279 可程式設計鍵盤

- 8257 DMA 控制器

- 微處理器常用資源

- 微處理器 - 快速指南

- 微處理器 - 常用資源

- 微處理器 - 討論

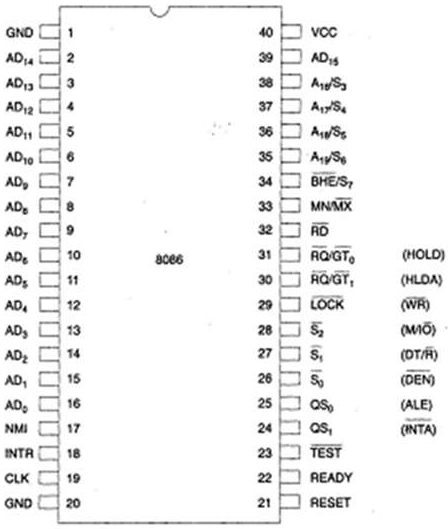

微處理器 - 8086 引腳配置

8086 是第一個採用 40 引腳 DIP(雙列直插式封裝)晶片的 16 位微處理器。現在讓我們詳細討論 8086 微處理器的引腳配置。

8086 引腳圖

以下是 8086 微處理器的引腳圖:

現在讓我們詳細討論這些訊號:

電源和頻率訊號

它使用 5V 直流電源在 VCC 引腳 40 供電,並在 VSS 引腳 1 和 20 接地。

時鐘訊號

時鐘訊號透過 19 號引腳提供。它為處理器的操作提供定時。不同版本的頻率不同,例如 5MHz、8MHz 和 10MHz。

地址/資料匯流排

AD0-AD15。這是 16 位地址/資料匯流排。AD0-AD7 傳輸低位位元組資料,AD8-AD15 傳輸高位位元組資料。在第一個時鐘週期,它傳輸 16 位地址,之後它傳輸 16 位資料。

地址/狀態匯流排

A16-A19/S3-S6。這是 4 位地址/狀態匯流排。在第一個時鐘週期,它傳輸 4 位地址,之後它傳輸狀態訊號。

S7/BHE

BHE 代表匯流排高位使能。它位於 34 號引腳,用於指示使用資料匯流排 D8-D15 傳輸資料。此訊號在第一個時鐘週期為低電平,之後變為有效。

讀 ($\overline{RD}$)

它位於 32 號引腳,用於讀取操作的讀取訊號。

就緒

它位於 22 號引腳。它是 I/O 裝置的資料傳輸確認訊號。它是高電平有效訊號。當它為高電平時,表示裝置已準備好傳輸資料。當它為低電平時,表示等待狀態。

復位

它位於 21 號引腳,用於重新啟動執行。它使處理器立即終止其當前活動。此訊號在前 4 個時鐘週期內為高電平,以復位微處理器。

INTR

它位於 18 號引腳。這是一箇中斷請求訊號,在每條指令的最後一個時鐘週期進行取樣,以確定處理器是否將其視為中斷。

NMI

它代表非遮蔽中斷,位於 17 號引腳。它是一個邊沿觸發的輸入,它向微處理器發出中斷請求。

$\overline{TEST}$

此訊號類似於等待狀態,位於 23 號引腳。當此訊號為高電平時,處理器必須等待空閒狀態,否則執行繼續。

MN/$\overline{MX}$

它代表最小/最大模式,位於 33 號引腳。它指示處理器要以哪種模式執行;當它為高電平時,它以最小模式工作,反之亦然。

INTA

這是一箇中斷確認訊號,位於 24 號引腳。當微處理器接收到此訊號時,它會確認中斷。

ALE

它代表地址鎖存使能,位於 25 號引腳。每次處理器開始任何操作時都會產生一個正脈衝。此訊號表示地址/資料線上有有效地址。

DEN

它代表資料使能,位於 26 號引腳。它用於使能收發器 8286。收發器是一種用於從地址/資料匯流排分離資料的裝置。

DT/R

它代表資料傳輸/接收訊號,位於 27 號引腳。它決定資料透過收發器的流動方向。當它為高電平時,資料被傳輸出去,反之亦然。

M/IO

此訊號用於區分儲存器和 I/O 操作。當它為高電平時,表示 I/O 操作;當它為低電平時,表示儲存器操作。它位於 28 號引腳。

WR

它代表寫訊號,位於 29 號引腳。它用於根據 M/IO 訊號的狀態將資料寫入儲存器或輸出裝置。

HLDA

它代表保持確認訊號,位於 30 號引腳。此訊號確認 HOLD 訊號。

HOLD

此訊號指示處理器外部裝置正在請求訪問地址/資料匯流排。它位於 31 號引腳。

QS1 和 QS0

這些是佇列狀態訊號,位於 24 號和 25 號引腳。這些訊號提供指令佇列的狀態。它們的狀態如以下表格所示:

| QS0 | QS1 | 狀態 |

|---|---|---|

| 0 | 0 | 無操作 |

| 0 | 1 | 佇列中的操作碼的第一個位元組 |

| 1 | 0 | 清空佇列 |

| 1 | 1 | 佇列中的後續位元組 |

S0、S1、S2

這些是狀態訊號,提供操作的狀態,由匯流排控制器 8288 用於生成儲存器和 I/O 控制訊號。它們位於 26 號、27 號和 28 號引腳。以下是顯示其狀態的表格:

| S2 | S1 | S0 | 狀態 |

|---|---|---|---|

| 0 | 0 | 0 | 中斷確認 |

| 0 | 0 | 1 | I/O 讀取 |

| 0 | 1 | 0 | I/O 寫入 |

| 0 | 1 | 1 | 暫停 |

| 1 | 0 | 0 | 操作碼提取 |

| 1 | 0 | 1 | 儲存器讀取 |

| 1 | 1 | 0 | 儲存器寫入 |

| 1 | 1 | 1 | 被動 |

LOCK

當此訊號有效時,它指示其他處理器不要請求 CPU 釋放系統匯流排。它透過在任何指令上使用 LOCK 字首來啟用,位於 29 號引腳。

RQ/GT1 和 RQ/GT0

這些是由其他處理器請求 CPU 釋放系統匯流排的請求/授權訊號。當 CPU 接收到訊號時,它會發送確認。RQ/GT0 的優先順序高於 RQ/GT1。