- 8085 微處理器

- 微處理器 - 8085 架構

- 8085 引腳配置

- 定址方式和中斷

- 8085 指令集

- 多處理器配置

- 配置概述

- 8087 數值資料處理器

- I/O 介面

- I/O 介面概述

- 8279 可程式設計鍵盤

- 8257 DMA 控制器

- 微處理器有用資源

- 微處理器 - 快速指南

- 微處理器 - 有用資源

- 微處理器 - 討論

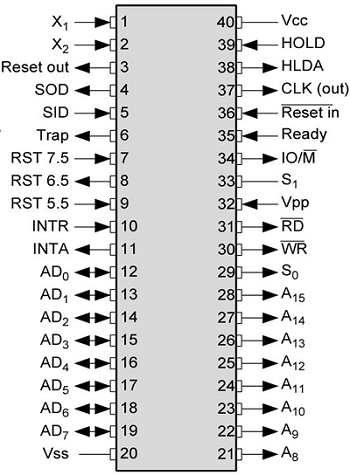

微處理器 - 8085 引腳配置

下圖顯示了 8085 微處理器的引腳圖:

8085 微處理器的引腳可以分為七組:

地址匯流排

A15-A8,它承載記憶體/IO 地址的最高 8 位。

資料匯流排

AD7-AD0,它承載最低 8 位地址和資料匯流排。

控制和狀態訊號

這些訊號用於識別操作的性質。有 3 個控制訊號和 3 個狀態訊號。

三個控制訊號分別是 RD、WR 和 ALE。

RD - 此訊號指示所選的 IO 或記憶體裝置將被讀取,並已準備好接收資料匯流排上可用的資料。

WR - 此訊號指示資料匯流排上的資料將被寫入選定的記憶體或 IO 位置。

ALE - 當微處理器啟動新操作時,它會生成一個正向脈衝。當脈衝變高時,它表示地址。當脈衝變低時,它表示資料。

三個狀態訊號分別是 IO/M、S0 和 S1。

IO/M

此訊號用於區分 IO 和記憶體操作,即當它為高電平時表示 IO 操作,當它為低電平時表示記憶體操作。

S1 和 S0

這些訊號用於識別當前操作的型別。

電源

有 2 個電源訊號 - VCC 和 VSS。VCC 表示 +5v 電源,VSS 表示接地訊號。

時鐘訊號

有 3 個時鐘訊號,即 X1、X2、CLK OUT。

X1、X2 - 一個晶體(RC、LC 網路)連線到這兩個引腳,並用於設定內部時鐘發生器的頻率。此頻率在內部除以 2。

CLK OUT - 此訊號用作連線到微處理器的裝置的系統時鐘。

中斷和外部發起的訊號

中斷是由外部裝置生成的訊號,請求微處理器執行任務。有 5 箇中斷訊號,即 TRAP、RST 7.5、RST 6.5、RST 5.5 和 INTR。我們將在中斷部分詳細討論中斷。

INTA - 它是中斷確認訊號。

RESET IN - 此訊號用於透過將程式計數器設定為零來複位微處理器。

RESET OUT - 當微處理器復位時,此訊號用於復位所有連線的裝置。

READY - 此訊號指示裝置已準備好傳送或接收資料。如果 READY 為低電平,則 CPU 必須等待 READY 變為高電平。

HOLD - 此訊號指示另一個主裝置正在請求使用地址和資料匯流排。

HLDA(HOLD 確認) - 它指示 CPU 已收到 HOLD 請求,並且將在下一個時鐘週期釋放匯流排。在 HOLD 訊號移除後,HLDA 設定為低電平。

序列 I/O 訊號

有 2 個序列訊號,即 SID 和 SOD,這些訊號用於序列通訊。

SOD(序列輸出資料線) - 輸出 SOD 根據 SIM 指令設定/復位。

SID(序列輸入資料線) - 每當執行 RIM 指令時,此線上的資料就會載入到累加器中。