- 8085 微處理器

- 微處理器 - 8085 架構

- 8085 引腳配置

- 定址方式和中斷

- 8085 指令集

- 多處理器配置

- 配置概述

- 8087 數值資料處理器

- I/O 介面

- I/O 介面概述

- 8279 可程式設計鍵盤

- 8257 DMA 控制器

- 微處理器有用資源

- 微處理器 - 快速指南

- 微處理器 - 有用資源

- 微處理器 - 討論

8255A - 可程式設計外圍介面

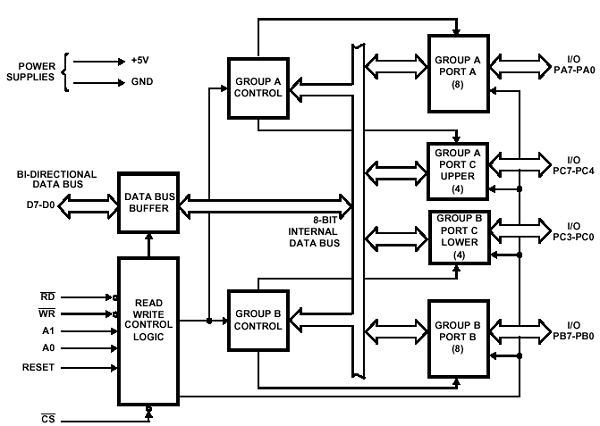

8255A 是一款通用的可程式設計 I/O 裝置,設計用於在特定條件下根據需要將資料從 I/O 傳輸到中斷 I/O。它幾乎可以與任何微處理器一起使用。

它包含三個 8 位雙向 I/O 埠(24 個 I/O 線),可以根據需要進行配置。

8255A 的埠

8255A 有三個埠,即埠 A、埠 B 和埠 C。

埠 A 包含一個 8 位輸出鎖存器/緩衝器和一個 8 位輸入緩衝器。

埠 B 與埠 A 類似。

埠 C 可以透過控制字分成兩部分,即埠 C 下半部分 (PC0-PC3) 和埠 C 上半部分 (PC7-PC4)。

這三個埠進一步分為兩組,即 A 組包括埠 A 和埠 C 上半部分。B 組包括埠 B 和埠 C 下半部分。這兩組可以用三種不同的模式程式設計,即第一種模式稱為模式 0,第二種模式稱為模式 1,第三種模式稱為模式 2。

工作模式

8255A 有三種不同的工作模式:

模式 0 - 在此模式下,埠 A 和 B 用作兩個 8 位埠,埠 C 用作兩個 4 位埠。每個埠可以程式設計為輸入模式或輸出模式,其中輸出是鎖存的,輸入不是鎖存的。埠沒有中斷能力。

模式 1 - 在此模式下,埠 A 和 B 用作 8 位 I/O 埠。它們可以配置為輸入或輸出埠。每個埠使用埠 C 中的三條線作為握手訊號。輸入和輸出是鎖存的。

模式 2 - 在此模式下,埠 A 可以配置為雙向埠,埠 B 可以配置為模式 0 或模式 1。埠 A 使用埠 C 中的五個訊號作為資料傳輸的握手訊號。埠 C 中剩餘的三個訊號可以用作簡單的 I/O 或埠 B 的握手訊號。

8255A 的特點

8255A 的主要特點如下:

它包含 3 個 8 位 IO 埠,即 PA、PB 和 PC。

地址/資料匯流排必須在外部進行多路分解。

它與 TTL 相容。

它具有改進的直流驅動能力。

8255 架構

下圖顯示了 8255A 的架構:

廣告