- 8085 微處理器

- 微處理器 - 8085 架構

- 8085 引腳配置

- 定址方式和中斷

- 8085 指令集

- 多處理器配置

- 配置概述

- 8087 數值資料處理器

- I/O 介面

- I/O 介面概述

- 8279 可程式設計鍵盤

- 8257 DMA 控制器

- 微處理器常用資源

- 微處理器 - 快速指南

- 微處理器 - 常用資源

- 微處理器 - 討論

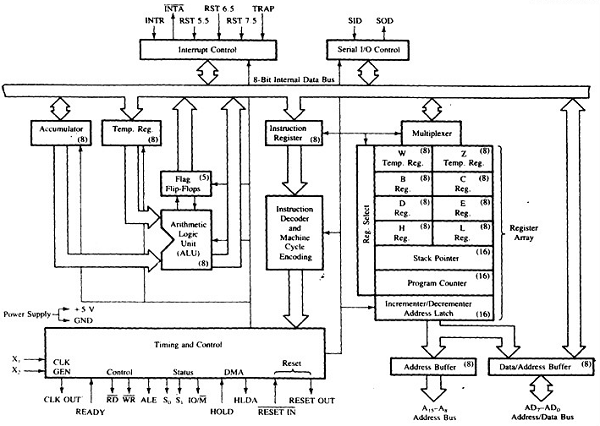

微處理器 - 8085 架構

8085 讀作“八十零五”微處理器。它是由英特爾公司於 1977 年使用 NMOS 技術設計的 8 位微處理器。

它具有以下配置:

- 8 位資料匯流排

- 16 位地址匯流排,最多可定址 64KB

- 一個 16 位程式計數器

- 一個 16 位堆疊指標

- 六個 8 位暫存器,成對排列:BC、DE、HL

- 需要 +5V 電源,在 3.2MHz 單相時鐘下工作

它用於洗衣機、微波爐、手機等。

8085 微處理器 – 功能單元

8085 包含以下功能單元:

累加器

這是一個 8 位暫存器,用於執行算術、邏輯、I/O 和 LOAD/STORE 操作。它連線到內部資料匯流排和 ALU。

算術邏輯單元

顧名思義,它對 8 位資料執行算術和邏輯運算,例如加法、減法、AND、OR 等。

通用暫存器

8085 處理器中有 6 個通用暫存器,即 B、C、D、E、H 和 L。每個暫存器可以儲存 8 位資料。

這些暫存器可以成對工作以儲存 16 位資料,它們的配對組合如下:B-C、D-E 和 H-L。

程式計數器

這是一個 16 位暫存器,用於儲存要執行的下一條指令的記憶體地址位置。每執行一條指令,微處理器都會遞增程式計數器,以便程式計數器指向將要執行的下一條指令的記憶體地址。

堆疊指標

它也是一個 16 位暫存器,像堆疊一樣工作,在 push 和 pop 操作期間始終遞增/遞減 2。

臨時暫存器

這是一個 8 位暫存器,它儲存算術和邏輯運算的臨時資料。

標誌暫存器

這是一個 8 位暫存器,具有五個 1 位觸發器,根據儲存在累加器中的結果儲存 0 或 1。

這五個觸發器是:

- 符號 (S)

- 零 (Z)

- 輔助進位 (AC)

- 奇偶 (P)

- 進位 (C)

其位位置如下表所示:

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| S | Z | AC | P | CY |

指令暫存器和譯碼器

這是一個 8 位暫存器。當從記憶體中取指令時,它將儲存在指令暫存器中。指令譯碼器對指令暫存器中存在的資訊進行譯碼。

定時和控制單元

它為微處理器提供定時和控制訊號以執行操作。以下是控制外部和內部電路的定時和控制訊號:

- 控制訊號:READY、RD’、WR’、ALE

- 狀態訊號:S0、S1、IO/M’

- DMA 訊號:HOLD、HLDA

- 復位訊號:RESET IN、RESET OUT

中斷控制

顧名思義,它在過程中控制中斷。當微處理器正在執行主程式並且發生中斷時,微處理器會將控制權從主程式轉移到處理傳入請求。請求完成後,控制權將返回主程式。

8085 微處理器中有 5 箇中斷訊號:INTR、RST 7.5、RST 6.5、RST 5.5、TRAP。

序列輸入/輸出控制

它使用這兩個指令控制序列資料通訊:SID(序列輸入資料)和 SOD(序列輸出資料)。

地址緩衝器和地址資料緩衝器

堆疊指標和程式計數器中儲存的內容被載入到地址緩衝器和地址資料緩衝器中以與 CPU 通訊。記憶體和 I/O 晶片連線到這些匯流排;CPU 可以與記憶體和 I/O 晶片交換所需的資料。

地址匯流排和資料匯流排

資料匯流排承載要儲存的資料。它是雙向的,而地址匯流排承載應儲存資料的地址,它是單向的。它用於傳輸資料和 I/O 裝置地址。

8085 架構

我們嘗試用下面的圖片描繪 8085 的架構: