- 8085 微處理器

- 微處理器 - 8085 架構

- 8085 引腳配置

- 定址模式和中斷

- 8085 指令集

- 多處理器配置

- 配置概述

- 8087 數值資料處理器

- I/O 介面

- I/O 介面概述

- 8279 可程式設計鍵盤

- 8257 DMA 控制器

- 微處理器有用資源

- 微處理器 - 快速指南

- 微處理器 - 有用資源

- 微處理器 - 討論

Intel 8253 - 可程式設計間隔定時器

Intel 8253 和 8254 是可程式設計間隔定時器 (PTI),專為微處理器設計,使用三個 16 位暫存器執行計時和計數功能。每個計數器有兩個輸入引腳,即時鐘和門,還有一個“OUT”輸出引腳。要操作計數器,需要在其暫存器中載入一個 16 位計數。根據命令,它開始遞減計數,直到達到 0,然後它生成一個脈衝,可用於中斷 CPU。

8253 和 8254 的區別

下表區分了 8253 和 8254 的特性:

| 8253 | 8254 |

|---|---|

| 其工作頻率為 0 - 2.6 MHz | 其工作頻率為 0 - 10 MHz |

| 它使用 N-MOS 技術 | 它使用 H-MOS 技術 |

| 不支援讀回命令 | 支援讀回命令 |

| 不能交錯讀取和寫入同一個計數器。 | 可以交錯讀取和寫入同一個計數器。 |

8253/54 的特性

8253/54 最突出的特性如下:

它具有三個獨立的 16 位向下計數器。

它可以處理從 DC 到 10 MHz 的輸入。

這三個計數器可以程式設計為二進位制或 BCD 計數。

它幾乎相容所有微處理器。

8254 有一個強大的命令,稱為讀回命令,允許使用者檢查計數值、程式設計模式、當前模式和計數器的當前狀態。

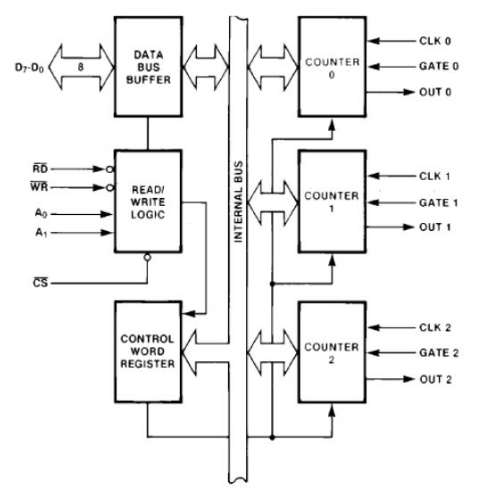

8254 架構

8254 的架構如下:

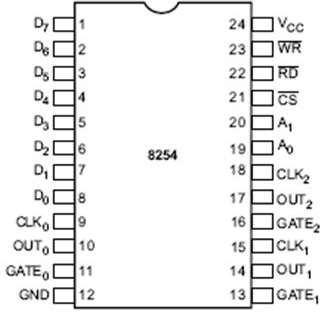

8254 引腳描述

以下是 8254 的引腳圖:

在上圖中,有三個計數器、一個數據匯流排緩衝器、讀/寫控制邏輯和一個控制暫存器。每個計數器有兩個輸入訊號 - 時鐘和門,以及一個輸出訊號 - OUT。

資料匯流排緩衝器

它是一個三態、雙向、8 位緩衝器,用於將 8253/54 介面到系統資料匯流排。它具有三個基本功能:

- 程式設計 8253/54 的模式。

- 載入計數暫存器。

- 讀取計數值。

讀/寫邏輯

它包括 5 個訊號,即 RD、WR、CS 和地址線 A0 & A1。在外設 I/O 模式下,RD 和 WR 訊號分別連線到 IOR 和 IOW。在儲存器對映 I/O 模式下,這些連線到 MEMR 和 MEMW。

CPU 的地址線 A0 & A1 連線到 8253/54 的 A0 和 A1 線,CS 連線到解碼地址。控制字暫存器和計數器根據 A0 & A1 線上的訊號進行選擇。

| A1 | A0 | 結果 |

|---|---|---|

| 0 | 0 | 計數器 0 |

| 0 | 1 | 計數器 1 |

| 1 | 0 | 計數器 2 |

| 1 | 1 | 控制字暫存器 |

| X | X | 無選擇 |

控制字暫存器

當 A0 & A1 線為邏輯 1 時訪問此暫存器。它用於寫入命令字,該命令字指定要使用的計數器、其模式以及讀或寫操作。下表顯示了各種控制輸入的結果。

| A1 | A0 | RD | WR | CS | 結果 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | 寫入計數器 0 |

| 0 | 1 | 1 | 0 | 0 | 寫入計數器 1 |

| 1 | 0 | 1 | 0 | 0 | 寫入計數器 2 |

| 1 | 1 | 1 | 0 | 0 | 寫入控制字 |

| 0 | 0 | 0 | 1 | 0 | 讀取計數器 0 |

| 0 | 1 | 0 | 1 | 0 | 讀取計數器 1 |

| 1 | 0 | 0 | 1 | 0 | 讀取計數器 2 |

| 1 | 1 | 0 | 1 | 0 | 無操作 |

| X | X | 1 | 1 | 0 | 無操作 |

| X | X | X | X | 1 | 無操作 |

計數器

每個計數器由一個單一的 16 位向下計數器組成,可以以二進位制或 BCD 方式操作。其輸入和輸出由控制字暫存器中儲存的模式選擇配置。程式設計師可以讀取任何三個計數器的內容,而不會影響正在進行的實際計數。