鎖相環積體電路

鎖相環(PLL)是線性系統中至關重要的模組之一。它在雷達、衛星、調頻等通訊系統中非常有用。

本章將詳細討論PLL和IC 565的框圖。

PLL框圖

鎖相環(PLL)主要由以下三個模組組成:

- 相位檢測器

- 有源低通濾波器

- 壓控振盪器(VCO)

PLL的框圖如下所示:

相位檢測器的輸出作為有源低通濾波器的輸入。類似地,有源低通濾波器的輸出作為VCO的輸入。

PLL的工作原理如下:

相位檢測器產生一個直流電壓,該電壓與輸入訊號(頻率為$f_{in}$)和反饋(輸出)訊號(頻率為$f_{out}$)之間的相位差成正比。

相位檢測器是一個乘法器,它在其輸出端產生兩個頻率分量:頻率$f_{in}$和$f_{out}$的和以及頻率$f_{in}$和$f_{out}$的差。

有源低通濾波器在其輸出端產生一個直流電壓,在消除相位檢測器輸出中存在的高頻分量後。它也放大訊號。

VCO產生一個具有特定頻率的訊號,當沒有輸入訊號施加到它時。可以透過向其施加直流電壓來將其頻率偏移到任一側。因此,頻率偏差與低通濾波器輸出端的直流電壓成正比。

上述操作持續進行,直到VCO頻率等於輸入訊號頻率。根據應用型別,我們可以使用有源低通濾波器的輸出或VCO的輸出。PLL應用廣泛,例如調頻解調器、時鐘發生器等。

PLL工作在以下三種模式之一:

- 自由執行模式

- 捕獲模式

- 鎖定模式

最初,當沒有輸入訊號施加到PLL時,PLL工作在自由執行模式。當施加具有某個頻率的輸入訊號到PLL時,VCO的輸出訊號頻率將開始變化。在此階段,據說PLL工作在捕獲模式。VCO的輸出訊號頻率將持續變化,直到它等於輸入訊號頻率。現在,據說PLL工作在鎖定模式。

IC 565

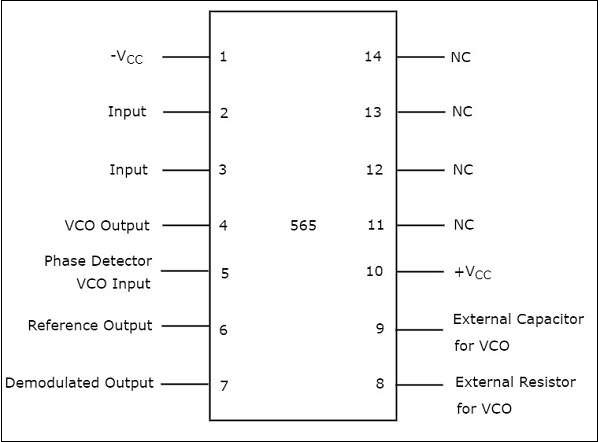

IC 565是最常用的鎖相環積體電路。它是一個14引腳雙列直插式封裝(DIP)。IC 565的引腳圖如下所示:

從上圖可以看出每個引腳的功能是不言自明的。在14個引腳中,只有10個引腳(引腳編號1到10)用於PLL的操作。因此,其餘4個引腳(引腳編號11到14)標記為NC(無連線)。

當引腳2和3接地時,VCO在IC 565的引腳4產生輸出。從數學上講,我們可以將VCO的輸出頻率$f_{out}$寫成。

$$f_{out}=\frac{0.25}{R_VC_V}$$

其中,

$R_{V}$是連線到引腳8的外部電阻

$C_{V}$是連線到引腳9的外部電容

透過選擇合適的$R_{V}$和$C_{V}$值,我們可以確定VCO的輸出頻率$f_{out}$。

引腳4和5需要用外部導線短接,以便VCO的輸出可以作為相位檢測器的輸入之一。

IC 565具有$3.6K\Omega$的內部電阻。為了與該內部電阻構成低通濾波器,必須在引腳7和10之間連線一個電容C。

請注意,根據要求,我們必須正確配置IC 565的引腳。