- 超大規模積體電路設計教程

- 超大規模積體電路設計 - 首頁

- 超大規模積體電路設計 - 數字系統

- 超大規模積體電路設計 - FPGA技術

- 超大規模積體電路設計 - MOS電晶體

- 超大規模積體電路設計 - MOS反相器

- 組合MOS邏輯電路

- 順序MOS邏輯電路

- VHDL程式設計

- VHDL - 簡介

- VHDL - 組合電路

- VHDL - 順序電路

- Verilog

- Verilog - 簡介

- 行為建模與時序

- 超大規模積體電路設計有用資源

- 超大規模積體電路設計 - 快速指南

- 超大規模積體電路設計 - 有用資源

- 超大規模積體電路設計 - 討論

超大規模積體電路設計 - 順序MOS邏輯電路

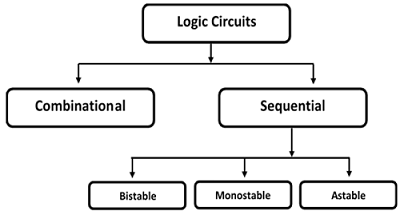

邏輯電路分為兩類:(a)組合電路和(b)順序電路。

在組合電路中,輸出僅取決於最新輸入的狀態。

在順序電路中,輸出不僅取決於最新的輸入,還取決於之前的輸入狀態。順序電路包含儲存單元。

順序電路有三種類型:

雙穩態 - 雙穩態電路有兩個穩定的工作點,並且將處於其中任何一個狀態。例如 - 儲存單元、鎖存器、觸發器和暫存器。

單穩態 - 單穩態電路只有一個穩定的工作點,即使它們暫時被擾動到相反的狀態,它們也會及時返回到其穩定的工作點。例如:定時器、脈衝發生器。

無穩態 - 電路沒有穩定的工作點,並在多個狀態之間振盪。例如 - 環形振盪器。

CMOS邏輯電路

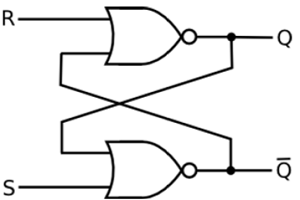

基於NOR門的SR鎖存器

如果置位輸入 (S) 等於邏輯“1”,而復位輸入等於邏輯“0”,則輸出 Q 將被強制為邏輯“1”。而$\overline{Q}$被強制為邏輯“0”。這意味著SR鎖存器將被置位,無論其先前狀態如何。

類似地,如果 S 等於“0”,而 R 等於“1”,則輸出 Q 將被強制為“0”,而$\overline{Q}$被強制為“1”。這意味著鎖存器被複位,無論其先前保持的狀態如何。最後,如果輸入 S 和 R 都等於邏輯“1”,則兩個輸出都將被強制為邏輯“0”,這與 Q 和$\overline{Q}$的互補性相沖突。

因此,在正常執行期間不允許使用此輸入組合。基於NOR門的SR鎖存器的真值表在表格中給出。

| S | R | Q | $\overline{Q}$ | 操作 |

|---|---|---|---|---|

| 0 | 0 | Q | $\overline{Q}$ | 保持 |

| 1 | 0 | 1 | 0 | 置位 |

| 0 | 1 | 0 | 1 | 復位 |

| 1 | 1 | 0 | 0 | 不允許 |

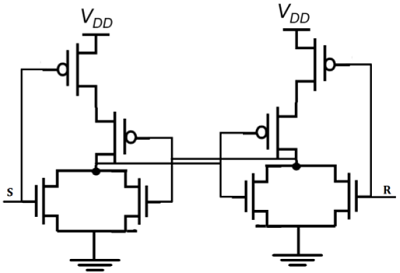

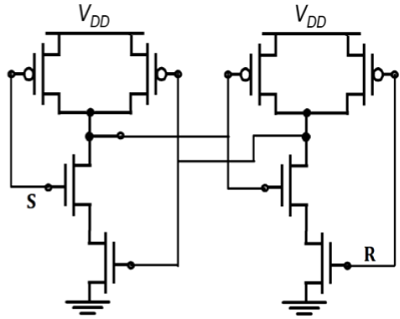

基於NOR門的CMOS SR鎖存器如下圖所示。

如果 S 等於 VOH,而 R 等於 VOL,則並聯連線的電晶體 M1 和 M2 將都導通。節點$\overline{Q}$上的電壓將假設 VOL = 0 的低邏輯電平。

同時,M3 和 M4 都關閉,這導致節點 Q 處的邏輯高電壓 VOH。如果 R 等於 VOH,而 S 等於 VOL,則 M1 和 M2 關閉,而 M3 和 M4 導通。

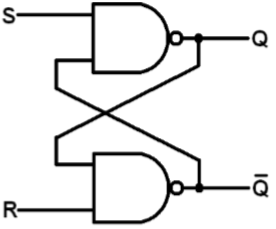

基於NAND門的SR鎖存器

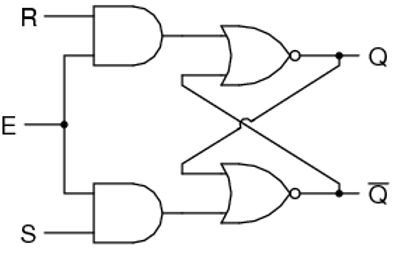

基於NAND門的SR鎖存器的框圖和門級原理圖如下圖所示。S 和 R 輸入端的小圓圈表示電路響應低電平有效輸入訊號。基於NAND門的SR鎖存器的真值表在表格中給出。

| S | R | Q | Q′ | |

| 0 | 0 | NC | NC | 無變化。鎖存器保持當前狀態。 |

| 1 | 0 | 1 | 0 | 鎖存器置位。 |

| 0 | 1 | 0 | 1 | 鎖存器復位。 |

| 1 | 1 | 0 | 0 | 無效狀態。 |

如果 S 變為 0(當 R = 1 時),Q 變為高電平,將$\overline{Q}$拉低,鎖存器進入置位狀態。

S = 0 則 Q = 1(如果 R = 1)

如果 R 變為 0(當 S = 1 時),Q 變為高電平,將$\overline{Q}$拉低,鎖存器復位。

R = 0 則 Q = 1(如果 S = 1)

保持狀態需要 S 和 R 都為高電平。如果 S = R = 0,則不允許輸出,因為它會導致不確定狀態。基於NAND門的CMOS SR鎖存器如下圖所示。

基於NAND門的耗盡型負載nMOS SR鎖存器如下圖所示。其操作與CMOS NAND SR鎖存器相似。CMOS電路實現具有低的靜態功耗和高的噪聲容限。

CMOS邏輯電路

帶時鐘的SR鎖存器

圖中顯示了一個添加了時鐘的基於NOR門的SR鎖存器。只有當CLK為高電平時,鎖存器才響應輸入S和R。

當CLK為低電平時,鎖存器保持其當前狀態。注意Q狀態變化:

- 當S在正CLK期間變高時。

- 在CLK低電平期間S&R變化後的前沿CLK邊沿。

- S在CLK為高電平期間的正毛刺。

- 當R在正CLK期間變高時。

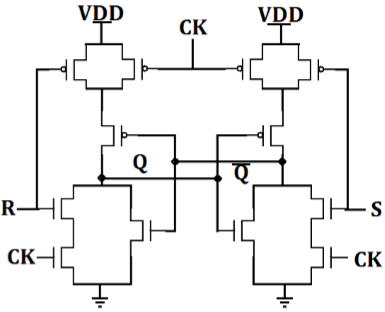

帶時鐘的基於NOR門的SR鎖存器的CMOS AOI實現如下圖所示。注意只需要12個電晶體。

當CLK為低電平時,N樹N中的兩個串聯端子斷開,而P樹中的兩個並聯電晶體導通,從而保持儲存單元中的狀態。

當時鍾為高電平時,電路簡化為基於NOR門的CMOS鎖存器,它將響應輸入S和R。

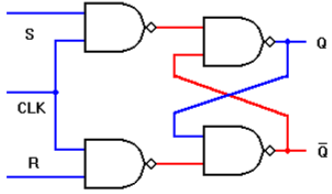

基於NAND門的帶時鐘的SR鎖存器

電路由四個NAND門實現。如果使用CMOS實現此電路,則需要16個電晶體。

- 只有當CLK為高電平時,鎖存器才響應S或R。

- 如果兩個輸入訊號和CLK訊號都為高電平有效:即,當CLK =“1”,S =“1”且R =“0”時,鎖存器輸出Q將被置位。

- 類似地,當CLK =“1”,S =“0”時,鎖存器將被複位,並且

當CLK為低電平時,鎖存器保持其當前狀態。

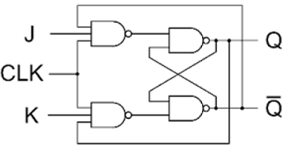

帶時鐘的JK鎖存器

上圖顯示了一個基於NAND門的帶時鐘的JK鎖存器。SR鎖存器的缺點是,當S和R都為高電平時,其輸出狀態變得不確定。JK鎖存器透過使用從輸出到輸入的反饋來消除這個問題,這樣真值表的所有輸入狀態都是允許的。如果J = K = 0,則鎖存器將保持其當前狀態。

如果J = 1且K = 0,則鎖存器將在下一個正跳變時鐘邊沿被置位,即Q = 1,$\overline{Q}$= 0。

如果J = 0且K = 1,則鎖存器將在下一個正跳變時鐘邊沿被複位,即Q = 1,$\overline{Q}$= 0。

如果J = K = 1,則鎖存器將在下一個正跳變時鐘邊沿翻轉。

帶時鐘的JK鎖存器的操作總結在下表中。

J |

K |

Q |

$\overline{Q}$ | S |

R |

Q |

$\overline{Q}$ | 操作 |

| 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 保持 |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 復位 |

| 1 | 0 | 1 | 0 | 0 | 1 | |||

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 | 置位 |

| 1 | 0 | 1 | 1 | 1 | 0 | |||

| 1 | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 翻轉 |

| 1 | 0 | 1 | 0 | 0 | 1 |

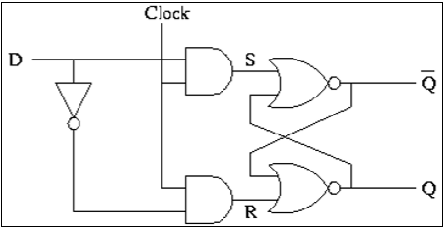

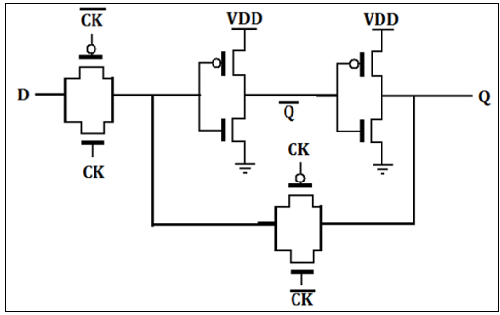

CMOS D鎖存器實現

D鎖存器通常使用傳輸門(TG)開關實現,如下圖所示。輸入TG由CLK啟用,而鎖存反饋環路TG由CLK啟用。當CLK為高電平時,接受輸入D。當CLK變為低電平時,輸入斷開,鎖存器設定為先前的數 據D。