- 超大規模積體電路設計教程

- 超大規模積體電路設計 - 首頁

- 超大規模積體電路設計 - 數字系統

- 超大規模積體電路設計 - FPGA技術

- 超大規模積體電路設計 - MOS電晶體

- 超大規模積體電路設計 - MOS反相器

- 組合MOS邏輯電路

- 時序MOS邏輯電路

- VHDL程式設計

- VHDL - 簡介

- VHDL - 組合電路

- VHDL - 時序電路

- Verilog

- Verilog - 簡介

- 行為建模與時序

- 超大規模積體電路設計有用資源

- 超大規模積體電路設計 - 快速指南

- 超大規模積體電路設計 - 有用資源

- 超大規模積體電路設計 - 討論

超大規模積體電路設計 - 數字系統

超大規模積體電路(VLSI)是透過將數千個電晶體整合到單個晶片上,從而建立積體電路(IC)的過程。VLSI始於20世紀70年代,當時複雜的半導體和通訊技術正在發展。微處理器是一種VLSI器件。

在引入VLSI技術之前,大多數IC的功能集有限。一個電子電路可能由CPU、ROM、RAM和其他粘合邏輯組成。VLSI允許IC設計人員將所有這些整合到一個晶片中。

電子行業在過去幾十年取得了驚人的增長,這主要得益於大規模整合技術和系統設計應用的快速發展。隨著超大規模整合(VLSI)設計的出現,積體電路(IC)在高效能計算、控制、電信、影像和影片處理以及消費電子產品中的應用數量正在以非常快的速度增長。

當前的尖端技術,例如高解析度和低位元率影片以及蜂窩通訊,為終端使用者提供了大量的應用、處理能力和便攜性。預計這種趨勢將迅速增長,這對VLSI設計和系統設計具有非常重要的意義。

VLSI設計流程

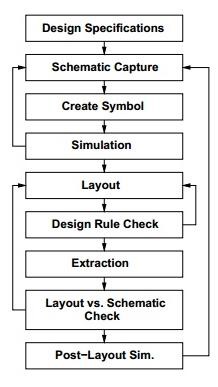

VLSI IC電路設計流程如下圖所示。設計中的各個層次用數字標註,各個模組顯示設計流程中的過程。

規範首先出現,它們抽象地描述了要設計的數字IC電路的功能、介面和架構。

然後建立行為描述,以從功能、效能、對給定標準的合規性和其他規範方面分析設計。

RTL描述使用HDL完成。對該RTL描述進行模擬以測試功能。從這裡開始,我們需要EDA工具的幫助。

然後使用邏輯綜合工具將RTL描述轉換為門級網表。門級網表是使用門和它們之間連線的電路描述,這些連線以滿足時序、功耗和麵積規範的方式製作。

最後,製作物理佈局,對其進行驗證,然後傳送到製造。

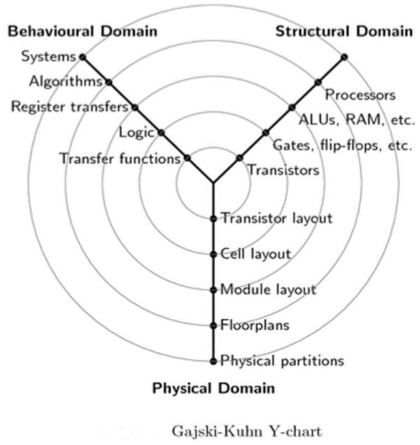

Y圖

Gajski-Kuhn Y圖是一個模型,它捕獲了設計半導體器件時的考慮因素。

Gajski-Kuhn Y圖的三個域位於徑向軸上。每個域都可以使用同心圓分成抽象級別。

在最高級別(外環),我們考慮晶片的架構;在較低級別(內環),我們依次將設計細化到更詳細的實現中 -

透過高階綜合或邏輯綜合過程,可以從行為描述建立結構描述。

透過佈局綜合,可以從結構描述建立物理描述。

設計層次結構-結構

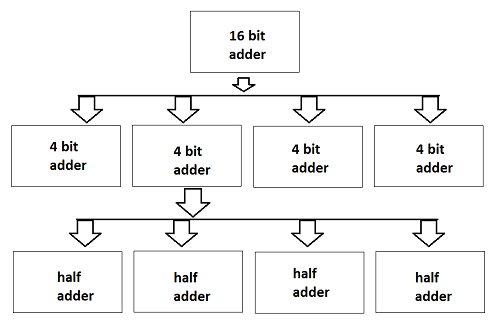

設計層次結構涉及“分而治之”的原則。它只不過是將任務分解成更小的任務,直到它達到最簡單的級別。此過程最合適,因為設計的最後演變變得非常簡單,因此其製造變得更容易。

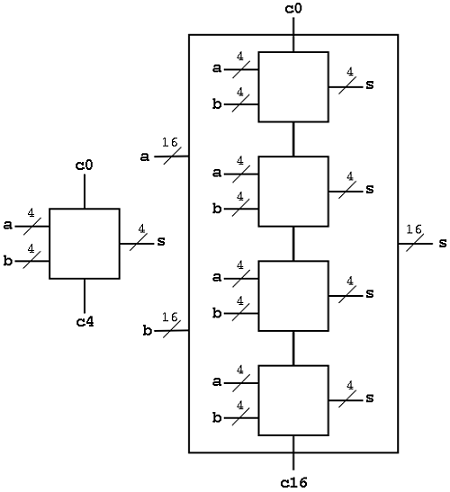

我們可以將給定任務設計到設計流程過程的域(行為、結構和幾何)。為了理解這一點,讓我們以設計一個16位加法器為例,如下圖所示。

這裡,整個16位加法器晶片被分成四個4位加法器模組。此外,將4位加法器進一步劃分為1位加法器或半加法器。1位加法是最簡單的設計過程,其內部電路也易於在晶片上製造。現在,連線所有最後的四個加法器,我們可以設計一個4位加法器,然後繼續設計一個16位加法器。