- VLSI設計教程

- VLSI設計 - 首頁

- VLSI設計 - 數字系統

- VLSI設計 - FPGA技術

- VLSI設計 - MOS電晶體

- VLSI設計 - MOS反相器

- 組合MOS邏輯電路

- 時序MOS邏輯電路

- VHDL程式設計

- VHDL - 簡介

- VHDL - 組合電路

- VHDL - 時序電路

- Verilog

- Verilog - 簡介

- 行為建模與時序

- VLSI設計有用資源

- VLSI設計 - 快速指南

- VLSI設計 - 有用資源

- VLSI設計 - 討論

組合MOS邏輯電路

組合邏輯電路或門,對多個輸入變數執行布林運算,並確定輸出作為輸入的布林函式,是所有數字系統的基本構建塊。我們將檢查簡單的電路配置,例如雙輸入與非門和或非門,然後將我們的分析擴充套件到多輸入電路結構的更一般情況。

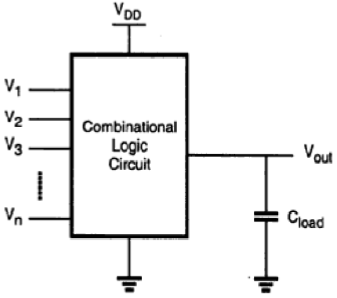

接下來,將以類似的方式介紹CMOS邏輯電路。我們將強調nMOS耗盡負載邏輯和CMOS邏輯電路之間的異同,並舉例說明CMOS門的優勢。在其最一般的形式中,執行布林函式的組合邏輯電路或門可以表示為多輸入、單輸出系統,如圖所示。

節點電壓(相對於接地電位)表示所有輸入變數。使用正邏輯約定,“1”的布林(或邏輯)值可以用VDD的高電壓表示,“0”的布林(或邏輯)值可以用0的低電壓表示。輸出節點載入了電容CL,它表示電路中寄生器件的組合電容。

CMOS邏輯電路

CMOS雙輸入或非門

該電路由並聯連線的n網路和串聯連線的互補p網路組成。輸入電壓VX和VY施加到一個nMOS電晶體和一個pMOS電晶體的門上。

當一個或兩個輸入都為高時,即當n網路在輸出節點和地之間形成導電路徑時,p網路被截止。如果兩個輸入電壓都為低,即n網路被截止,則p網路在輸出節點和電源電壓之間形成導電路徑。

對於任何給定的輸入組合,互補電路結構使得輸出透過低阻抗路徑連線到VDD或接地,並且對於任何輸入組合都不會在VDD和地之間建立直流電流路徑。CMOS雙輸入或非門的輸出電壓將獲得VOL = 0的邏輯低電壓和VOH = VDD的邏輯高電壓。開關閾值電壓Vth的方程由下式給出

$$V_{th}\left ( NOR2 \right ) = \frac{V_{T,n}+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+\frac{1}{2}\sqrt{\frac{k_{p}}{k_{n}}}}$$

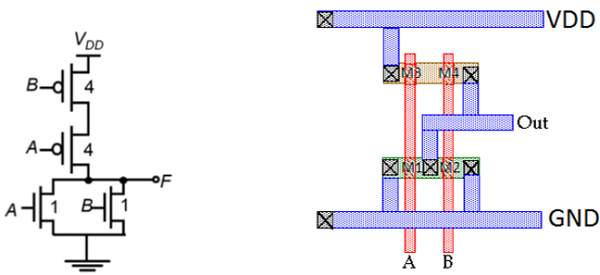

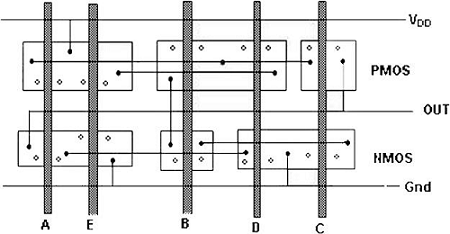

CMOS雙輸入或非門的佈局

該圖顯示了使用單層金屬和單層多晶矽的CMOS雙輸入或非門的示例佈局。此佈局的特徵為:

- 每個輸入的單根垂直多晶矽線

- 分別用於N和P器件的單個有源形狀

- 水平執行的金屬匯流排

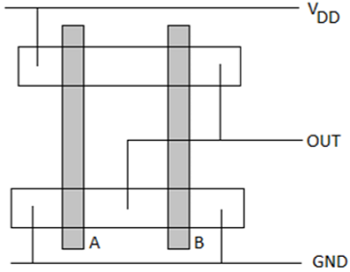

CMOS N0R2門的線框圖如下所示;它直接對應於佈局,但不包含W和L資訊。擴散區域由矩形表示,金屬連線和實線分別表示觸點,交叉陰影條表示多晶矽柱。線框圖可用於規劃最佳佈局拓撲。

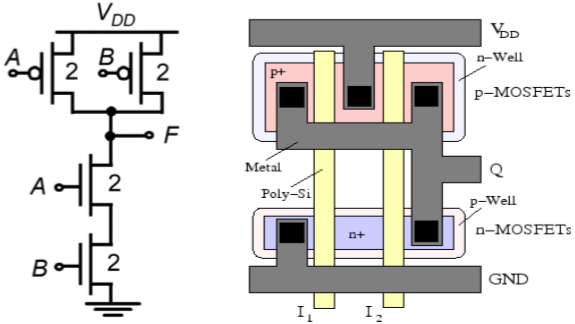

CMOS雙輸入與非門

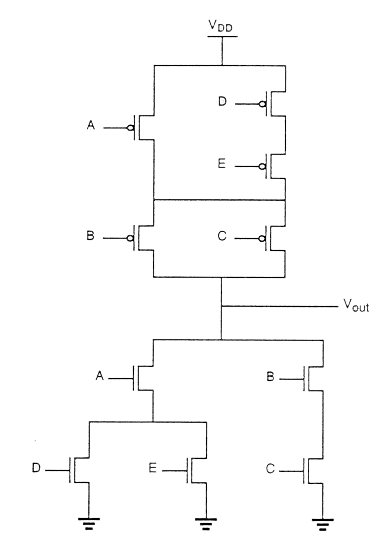

雙輸入CMOS與非門的電路圖如下所示。

該電路的工作原理與CMOS雙輸入或非門的工作原理完全對偶。如果兩個輸入電壓都為邏輯高,則由兩個串聯連線的nMOS電晶體組成的n網路將在輸出節點和地之間形成導電路徑。p網路中的兩個並聯連線的pMOS電晶體都將關閉。

對於所有其他輸入組合,一個或兩個pMOS電晶體將導通,而p網路被截止,從而在輸出節點和電源電壓之間形成電流路徑。該門的開關閾值獲得如下:

$$V_{th}\left ( NAND2 \right ) = \frac{V_{T,n}+2\sqrt{\frac{k_{p}}{k_{n}}\left ( V_{DD}-\left | V_{T,p} \right | \right )}}{1+2\sqrt{\frac{k_{p}}{k_{n}}}}$$

此佈局的特徵如下:

- 用於輸入的單根多晶矽線垂直穿過N和P有源區域。

- 單個有源形狀用於構建兩個nMOS器件和兩個pMOS器件。

- 電源佈線在佈局的頂部和底部水平執行。

- 輸出線水平執行,便於連線到相鄰電路。

複雜邏輯電路

NMOS耗盡負載複雜邏輯閘

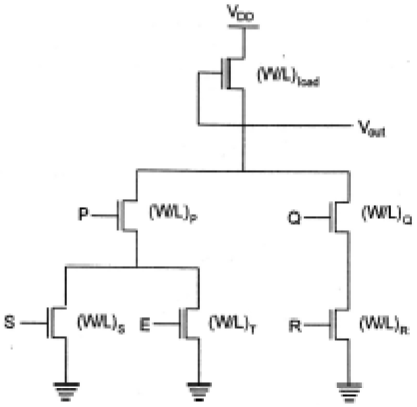

為了實現多個輸入變數的複雜函式,可以將為或非門和與非門開發的基本電路結構和設計原理擴充套件到複雜邏輯閘。能夠使用少量電晶體實現複雜邏輯函式是nMOS和CMOS邏輯電路最吸引人的特性之一。以下面的布林函式為例。

$$\overline{Z=P\left ( S+T \right )+QR}$$

用於實現此函式的nMOS耗盡負載複雜邏輯閘如圖所示。在此圖中,由三個驅動電晶體組成的左側nMOS驅動分支用於執行邏輯函式P (S + T),而右側分支執行函式QR。透過將兩個分支並聯連線,並將負載電晶體置於輸出節點和電源電壓VDD之間,我們獲得了給定的複雜函式。每個輸入變數僅分配給一個驅動器。

檢查電路拓撲結構可以得到下拉網路的簡單設計原則:

- 或運算由並聯連線的驅動器執行。

- 與運算由串聯連線的驅動器執行。

- 反轉由MOS電路操作的性質提供。

如果實現該函式的電路中所有輸入變數都為邏輯高,則由五個nMOS電晶體組成的下拉網路的等效驅動器(W/L)比率為

$$\frac{W}{L}=\frac{1}{\frac{1}{\left ( W/L \right )Q}+\frac{1}{\left ( W/L \right )R}}+\frac{1}{\frac{1}{\left ( W/L \right )P}+\frac{1}{\left ( W/L \right )S+\left ( W/L \right )Q}}$$

複雜CMOS邏輯閘

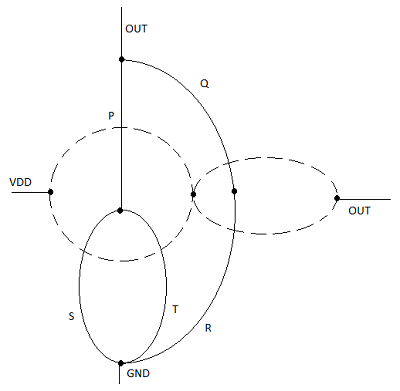

n網路或下拉網路的實現基於與nMOS耗盡負載複雜邏輯閘相同的基本設計原則。pMOS上拉網路必須是n網路的對偶網路。

這意味著nMOS網路中的所有並聯連線都將對應於pMOS網路中的串聯連線,並且nMOS網路中的所有串聯連線都對應於pMOS網路中的並聯連線。該圖顯示了從n網路(下拉)圖構建對偶p網路(上拉)圖的簡單構造。

下拉網路中的每個驅動電晶體由ai表示,每個節點由下拉圖中的一個頂點表示。接下來,在下拉圖中的每個封閉區域內建立一個新的頂點,並且相鄰的頂點透過邊連線,這些邊僅穿過下拉圖中的每條邊一次。此新圖顯示了上拉網路。

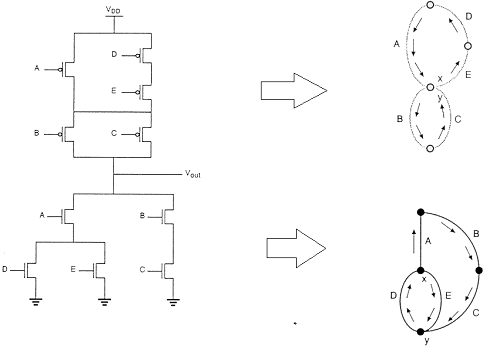

使用尤拉圖方法的佈局技術

該圖顯示了複雜函式的CMOS實現及其使用任意門排序完成的線框圖,這為CMOS門提供了非常非最佳的佈局。

在這種情況下,多晶矽柱之間的間距必須允許它們之間進行擴散到擴散的間距。這當然會消耗相當多的額外矽面積。

透過使用尤拉路徑,我們可以獲得最佳佈局。尤拉路徑定義為一條不間斷的路徑,該路徑恰好遍歷圖的每條邊(分支)一次。在下拉樹圖和上拉樹圖中找到具有相同輸入排序的尤拉路徑。