- 超大規模積體電路設計教程

- 超大規模積體電路設計 - 首頁

- 超大規模積體電路設計 - 數字系統

- 超大規模積體電路設計 - FPGA技術

- 超大規模積體電路設計 - MOS電晶體

- 超大規模積體電路設計 - MOS反相器

- 組合MOS邏輯電路

- 時序MOS邏輯電路

- VHDL程式設計

- VHDL - 簡介

- VHDL - 組合電路

- VHDL - 時序電路

- Verilog

- Verilog - 簡介

- 行為建模與時序

- 超大規模積體電路設計有用資源

- 超大規模積體電路設計 - 快速指南

- 超大規模積體電路設計 - 有用資源

- 超大規模積體電路設計 - 討論

超大規模積體電路設計 - MOS反相器

反相器確實是所有數字設計的核心。一旦清楚地理解了它的工作原理和特性,設計更復雜的結構,如與非門、加法器、乘法器和微處理器,就會大大簡化。這些複雜電路的電氣行為幾乎可以完全透過外推反相器的結果來推導。

反相器的分析可以擴充套件到解釋更復雜門(如與非門、或非門或異或門)的行為,而這些門反過來又構成乘法器和處理器等模組的構建塊。在本章中,我們將重點關注反相器門的單一實現形式,即靜態CMOS反相器——簡稱CMOS反相器。這當然是目前最流行的,因此值得我們特別關注。

工作原理

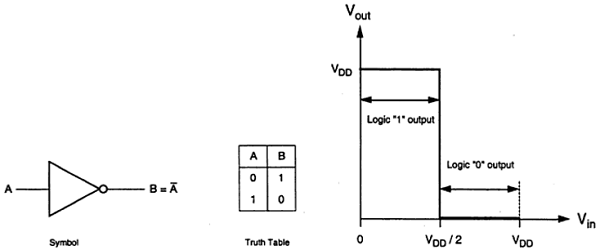

理想反相器的邏輯符號和真值表如下所示。這裡A是輸入,B是反相輸出,由它們的節點電壓表示。使用正邏輯,邏輯1的布林值由Vdd表示,邏輯0由0表示。Vth是反相器閾值電壓,等於Vdd /2,其中Vdd是輸出電壓。

當輸入小於Vth時,輸出從0切換到Vdd。因此,對於0<Vin<Vth,輸出等於邏輯0輸入;對於Vth<Vin< Vdd,輸出等於反相器的邏輯1輸入。

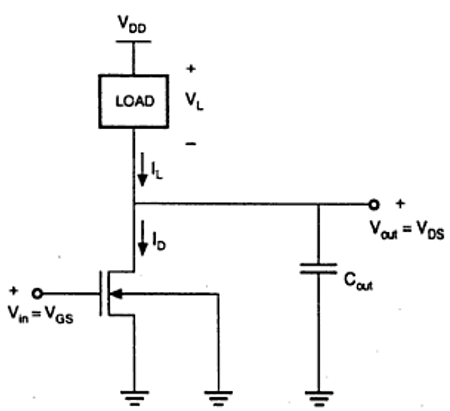

圖中所示的特性是理想的。nMOS反相器的通用電路結構如下圖所示。

從上圖可以看出,反相器的輸入電壓等於nMOS電晶體的柵源電壓,反相器的輸出電壓等於nMOS電晶體的漏源電壓。nMOS的源襯電壓也稱為電晶體的驅動器,其接地;因此VSS = 0。輸出節點連線到用於VTC的集總電容。

電阻負載反相器

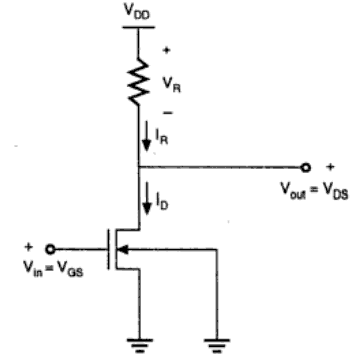

電阻負載反相器的基本結構如下圖所示。這裡,增強型nMOS充當驅動電晶體。負載由一個簡單的線性電阻RL組成。電路的電源是VDD,漏極電流ID等於負載電流IR。

電路工作

當驅動電晶體的輸入小於閾值電壓VTH (Vin < VTH)時,驅動電晶體處於截止區域,不導通任何電流。因此,負載電阻上的電壓降為零,輸出電壓等於VDD。現在,當輸入電壓進一步增加時,驅動電晶體將開始導通非零電流,nMOS進入飽和區。

數學上,

$$I_{D} = \frac{K_{n}}{2}\left [ V_{GS}-V_{TO} \right ]^{2}$$

進一步增加輸入電壓,驅動電晶體將進入線性區,驅動電晶體的輸出減小。

$$I_{D} = \frac{K_{n}}{2}2\left [ V_{GS}-V_{TO} \right ]V_{DS}-V_{DS}^{2}$$

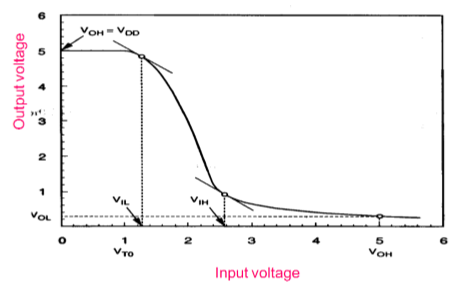

下圖所示的電阻負載反相器的VTC指示驅動電晶體的工作模式和電壓點。

帶N型MOSFET負載的反相器

使用MOSFET作為負載器件的主要優點是電晶體佔用的矽面積小於電阻負載佔用的面積。這裡,MOSFET是有源負載,具有有源負載的反相器比具有電阻負載的反相器具有更好的效能。

增強型負載NMOS

圖中顯示了兩個具有增強型負載器件的反相器。負載電晶體可以在飽和區或線性區工作,這取決於施加到其柵極端的偏置電壓。飽和增強型負載反相器如圖(a)所示。它只需要單電源和簡單的製造工藝,因此VOH 限制在VDD − VT。

線性增強型負載反相器如圖(b)所示。它始終線上性區工作;因此VOH 電平等於VDD。

與飽和增強型反相器相比,線性負載反相器具有更高的噪聲容限。但是,線性增強型反相器的缺點是它需要兩個獨立的電源,並且這兩個電路都存在功耗高的缺點。因此,增強型反相器不用於任何大規模數字應用。

耗盡型負載NMOS

增強型負載反相器的缺點可以透過使用耗盡型負載反相器來克服。與增強型負載反相器相比,耗盡型負載反相器需要更多的製造步驟來進行溝道注入以調整負載的閾值電壓。

耗盡型負載反相器的優點是:VTC轉換尖銳、噪聲容限更好、單電源和更小的整體佈局面積。

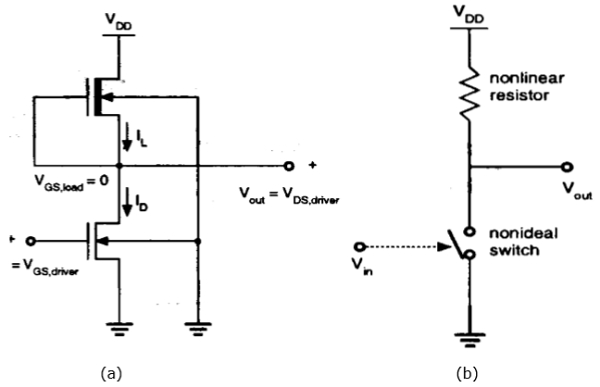

如圖所示,負載的柵極和源極端子相連;因此,VGS = 0。因此,負載的閾值電壓為負。因此,

$$V_{GS,load}> V_{T,load}$$ 成立

因此,無論輸入和輸出電壓電平如何,負載器件始終具有導電通道。

當負載電晶體處於飽和區時,負載電流由下式給出

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ -V_{T,load}\left ( V_{out} \right ) \right ]^{2}$$

當負載電晶體處於線性區時,負載電流由下式給出

$$I_{D,load} = \frac{K_{n,load}}{2}\left [ 2\left | V_{T,load}\left ( V_{out} \right ) \right |.\left ( V_{DD}-V_{out} \right )-\left ( V_{DD}-V_{out} \right )^{2} \right ]$$

耗盡型負載反相器的電壓傳輸特性如下圖所示:

CMOS反相器 – 電路、工作原理和描述

CMOS反相器電路如下圖所示。這裡,nMOS和pMOS電晶體充當驅動電晶體;當一個電晶體導通時,另一個電晶體截止。

這種配置稱為互補MOS (CMOS)。輸入連線到兩個電晶體的柵極端子,以便可以直接用輸入電壓驅動兩者。nMOS的襯底連線到地,pMOS的襯底連線到電源VDD。

因此,兩個電晶體的VSB = 0。

$$V_{GS,n}=V_{in}$$

$$V_{DS,n}=V_{out}$$

而且,

$$V_{GS,p}=V_{in}-V_{DD}$$

$$V_{DS,p}=V_{out}-V_{DD}$$

當nMOS的輸入小於閾值電壓(Vin < VTO,n)時,nMOS截止,pMOS處於線性區。因此,兩個電晶體的漏極電流都為零。

$$I_{D,n}=I_{D,p}=0$$

因此,輸出電壓VOH等於電源電壓。

$$V_{out}=V_{OH}=V_{DD}$$

當輸入電壓大於VDD + VTO,p時,pMOS電晶體處於截止區,nMOS處於線性區,因此兩個電晶體的漏極電流都為零。

$$I_{D,n}=I_{D,p}=0$$

因此,輸出電壓VOL等於零。

$$V_{out}=V_{OL}=0$$

如果Vin > VTO並且滿足以下條件,則nMOS工作在飽和區。

$$V_{DS,n}\geq V_{GS,n}-V_{TO,n} $$

$$V_{out}\geq V_{in}-V_{TO,n} $$

如果Vin < VDD + VTO,p並且滿足以下條件,則pMOS工作在飽和區。

$$V_{DS,p}\leq V_{GS,p}-V_{TO,p} $$

$$V_{out}\leq V_{in}-V_{TO,p} $$

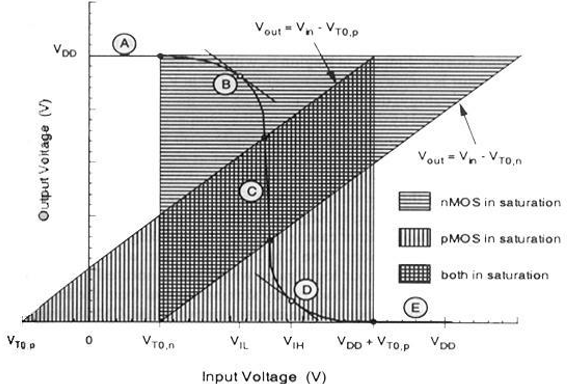

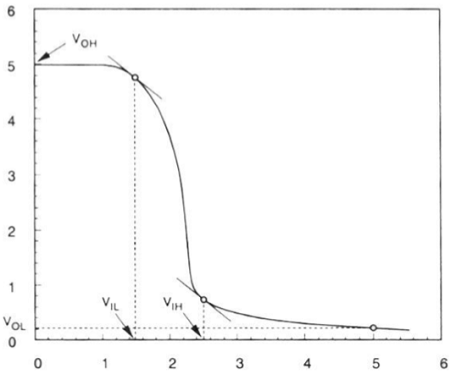

對於不同的輸入電壓值,下面列出了兩個電晶體的工作區域。

| 區域 | Vin | Vout | nMOS | pMOS |

|---|---|---|---|---|

| A | < VTO, n | VOH | 截止 | 線性 |

| B | VIL | 高 ≈ VOH | 飽和 | 線性 |

| C | Vth | Vth | 飽和 | 飽和 |

| D | VIH | 低 ≈ VOL | 線性 | 飽和 |

| E | > (VDD + VTO, p) | VOL | 線性 | 截止 |

CMOS的VTC如下圖所示: