- 超大規模積體電路設計教程

- 超大規模積體電路設計 - 首頁

- 超大規模積體電路設計 - 數字系統

- 超大規模積體電路設計 - FPGA 技術

- 超大規模積體電路設計 - MOS 電晶體

- 超大規模積體電路設計 - MOS 反相器

- 組合 MOS 邏輯電路

- 時序 MOS 邏輯電路

- VHDL 程式設計

- VHDL - 簡介

- VHDL - 組合電路

- VHDL - 時序電路

- Verilog

- Verilog - 簡介

- 行為建模與時序

- 超大規模積體電路設計實用資源

- 超大規模積體電路設計 - 快速指南

- 超大規模積體電路設計 - 有用資源

- 超大規模積體電路設計 - 討論

超大規模積體電路設計 - FPGA 技術

FPGA – 簡介

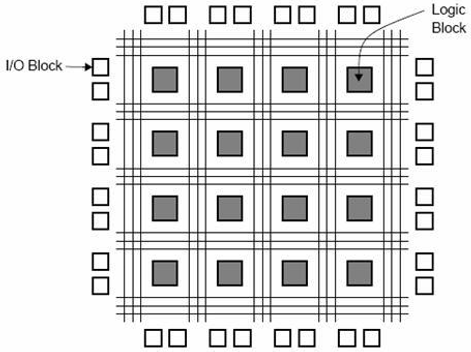

FPGA 的全稱是“現場可程式設計門陣列”。它包含從數萬到超過百萬個具有可程式設計互連的邏輯閘。可程式設計互連可供使用者或設計人員輕鬆執行給定功能。下圖顯示了一個典型的 FPGA 晶片模型。有 I/O 塊,根據功能進行設計和編號。對於每個邏輯級組成的模組,都有CLB(可配置邏輯塊)。

CLB 執行賦予模組的邏輯運算。CLB 和 I/O 塊之間的互連藉助水平佈線通道、垂直佈線通道和 PSM(可程式設計多路複用器)實現。

它包含的 CLB 數量僅決定 FPGA 的複雜性。CLB 和 PSM 的功能由 VHDL 或任何其他硬體描述語言設計。程式設計後,CLB 和 PSM 被放置在晶片上並透過佈線通道相互連線。

優點

- 它只需要很少的時間;從設計過程到功能晶片。

- 它不涉及任何物理製造步驟。

- 唯一的缺點是,它比其他方式更昂貴。

門陣列設計

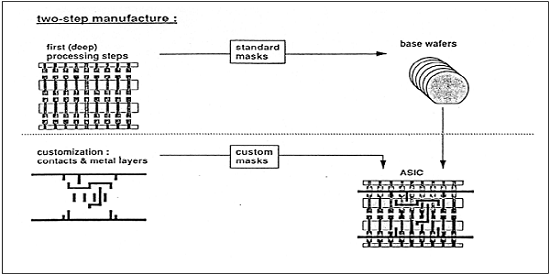

就快速原型設計能力而言,門陣列 (GA) 排名第二,僅次於 FPGA。雖然使用者程式設計對於 FPGA 晶片的設計實現非常重要,但 GA 使用金屬掩膜設計和處理。門陣列實現需要兩步製造過程。

第一階段在每個 GA 晶片上產生一系列未連線的電晶體。這些未連線的晶片可以儲存起來以備以後定製,透過定義陣列中電晶體之間的金屬互連來完成定製。金屬互連的圖案化在晶片製造過程結束時完成,因此週轉時間仍然很短,從幾天到幾周不等。下圖顯示了門陣列實現的基本處理步驟。

典型的門陣列平臺使用稱為通道的專用區域,用於 MOS 電晶體行或列之間的單元間佈線。它們簡化了互連。執行基本邏輯閘的互連模式儲存在庫中,然後可以根據網表使用這些模式來自定義未連線電晶體的行。

在大多數現代 GA 中,使用多個金屬層進行通道佈線。透過使用多個互連層,可以在有源單元區域上實現佈線;這樣就可以像在“門海”(SOG)晶片中一樣去除佈線通道。在這裡,整個晶片表面都覆蓋著未連線的 nMOS 和 pMOS 電晶體。可以使用金屬掩膜定製相鄰電晶體以形成基本邏輯閘。

對於單元間佈線,必須犧牲一些未連線的電晶體。這種設計風格使得互連具有更大的靈活性,並且通常具有更高的密度。GA 晶片利用率由使用的芯片面積除以總芯片面積來衡量。它高於 FPGA,晶片速度也是如此。

基於標準單元的設計

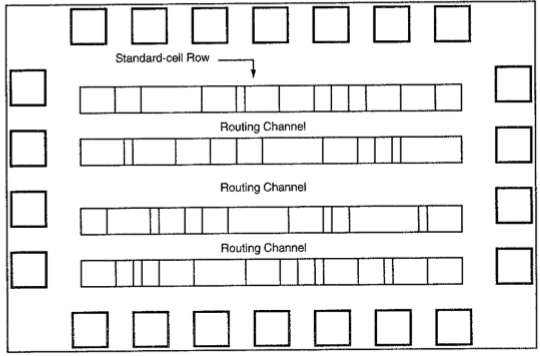

基於標準單元的設計需要開發完整的定製掩膜組。標準單元也稱為多晶矽單元。在這種方法中,所有常用的邏輯單元都已開發、表徵並存儲在標準單元庫中。

庫可能包含幾百個單元,包括反相器、與非門、或非門、複雜的 AOI、OAI 門、D 鎖存器和觸發器。每種門型別都可以實現多個版本,以提供對不同扇出足夠的驅動能力。反相器門可以具有標準尺寸、雙倍尺寸和四倍尺寸,以便晶片設計人員可以選擇合適的尺寸以獲得高的電路速度和佈局密度。

每個單元都根據幾個不同的表徵類別進行表徵,例如:

- 延遲時間與負載電容

- 電路模擬模型

- 時序模擬模型

- 故障模擬模型

- 用於佈局佈線的單元資料

- 掩膜資料

為了自動放置單元和佈線,每個單元佈局都設計成固定高度,以便可以並排繫結多個單元以形成行。電源和地軌平行於單元的上邊界和下邊界執行。這樣,相鄰單元共享一個公共電源匯流排和一個公共地匯流排。下圖是基於標準單元設計的樓層規劃圖。

全定製設計

在全定製設計中,整個掩膜設計都是全新的,無需使用任何庫。這種設計風格的開發成本正在上升。因此,設計重用的概念變得越來越流行,以減少設計週期時間和開發成本。

最難的全定製設計可能是儲存單元的設計,無論是靜態的還是動態的。對於邏輯晶片設計,可以使用同一晶片上不同設計風格的組合來獲得良好的協商,即標準單元、資料路徑單元和可程式設計邏輯陣列 (PLA)。

實際上,設計人員進行全定製佈局,即每個電晶體的幾何形狀、方向和位置。設計生產力通常非常低;通常每個設計人員每天只有幾十個電晶體。在數字 CMOS VLSI 中,由於高昂的勞動力成本,幾乎不使用全定製設計。這些設計風格包括大批次產品的設 計,例如儲存晶片、高效能微處理器和 FPGA。