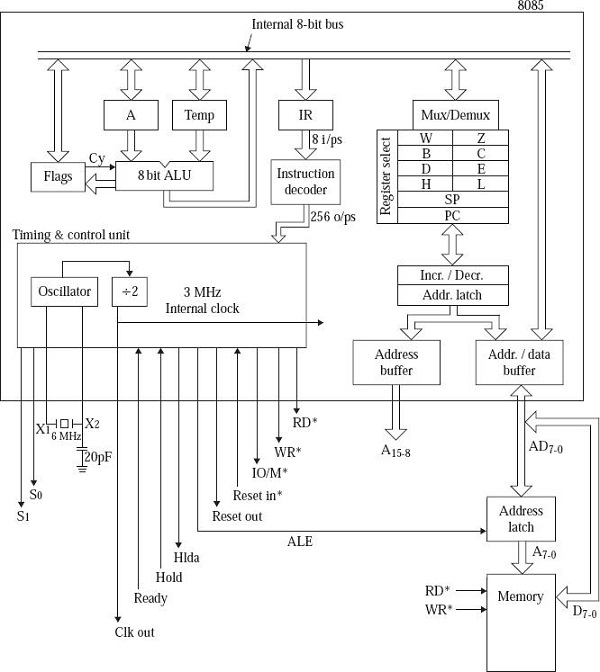

8085微處理器中的多路複用器/多路分解器

讓我們考慮要執行的指令為“MOV A, C”。在這種情況下,必須將暫存器C中的8位值移動到累加器暫存器。給定的暫存器組,即B、C、D、E、H和L,必須透過多路複用器(多輸入單輸出)或多路分解器(多路複用器的反向)連線到內部匯流排。負責執行工作的暫存器選擇特定的單元,並將相應的程式碼傳送到多路複用器,以便暫存器C的內容透過內部匯流排傳送到多路複用器。此後,累加器接收來自內部匯流排的資料。

讓我們考慮給定指令“MOV D, A”的整個執行過程。在這種情況下,累加器的位值被移動到暫存器D。8位值被髮送到累加器。暫存器B、C、D、E、H和L透過多路複用器/多路分解器連線到內部匯流排。給定的暫存器為多路分解器選擇相應的程式碼,以便名為D的暫存器從內部匯流排接收所有內容到多路分解器。實際上,基本概念在於,在多路複用器中,許多輸入合併形成一個輸出。而多路分解器則適用反向過程。因此,在地址緩衝區中,我們發現執行的算術和邏輯序列操作涉及兩個運算元,其中一個運算元由累加器提供,另一個運算元由臨時暫存器提供。例如,在加法過程中,對B暫存器的指令,所有內容都被故意移動到臨時暫存器,然後算術邏輯單元最終執行暫存器A和臨時暫存器的加法。與W和Z類似

廣告

資料結構

資料結構 網路

網路 RDBMS

RDBMS 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP