- 脈衝電路掃描電路

- 單結電晶體

- UJT 作為弛豫振盪器

- 脈衝電路 - 同步

- 脈衝電路 - 阻斷振盪器

- 脈衝電路取樣門

- 脈衝電路 - 取樣門

- 單向取樣門

- 單向多輸入

- 雙向取樣門

- 脈衝電路有用資源

- 脈衝電路 - 快速指南

- 脈衝電路 - 有用資源

- 脈衝電路 - 討論

單向多輸入

我們之前討論過的單向取樣閘電路只有一個輸入。在本章中,讓我們討論一些可以處理多個輸入訊號的單向取樣閘電路。

單向取樣閘電路由相同值的電容器和電阻組成。這裡考慮了一個具有兩個輸入的雙輸入單向二極體取樣門。在這個電路中,我們有兩個電容器和兩個相同值的電阻。它們分別連線到兩個二極體。

控制訊號施加在電阻上。輸出取自負載電阻兩端。下圖顯示了具有多個輸入訊號的單向二極體取樣門的電路圖。

當給出控制輸入時,

在 VC = V1(即傳輸期間),兩個二極體 D1 和 D2 都是正向偏置的。現在,輸出將是所有三個輸入的總和。

$$V_O = V_{S1} + V_{S2} + V_C$$

對於 V1 = 0v(這是理想值),

$$V_O = V_{S1} + V_{S2}$$

這裡有一個主要的限制,即在傳輸期間的任何時刻,只能施加一個輸入。這是該電路的一個缺點。

在非傳輸期間,

$$V_C = V_2$$

兩個二極體都將處於反向偏置狀態,這意味著開路。

這使得輸出

$$V_O = 0V$$

該電路的主要缺點是,隨著輸入數量的增加,電路的負載也會增加。可以透過另一個電路避免此限制,在該電路中,控制輸入在輸入訊號二極體之後給出。

基座降低

在瀏覽不同型別的取樣門及其產生的輸出時,我們在輸出波形中遇到了一個額外的電壓電平,稱為基座。這是不需要的,會產生一些噪聲。

閘電路中基座的降低

即使沒有施加輸入訊號,傳輸期間和非傳輸期間輸出訊號的差異也稱為基座。它可以是正基座或負基座。

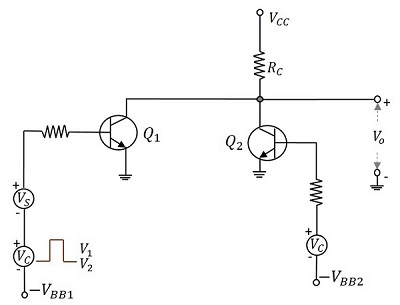

因此,它是由於門控電壓而觀察到的輸出,儘管輸入訊號不存在。這是不需要的,必須減少。下面的電路設計用於降低閘電路中的基座。

當施加控制訊號時,在傳輸期間,即在 V1 時,Q1 導通,Q2 關閉,並且 VCC 透過 RC 施加到 Q1。而在非傳輸期間,即在 V2 時,Q2 導通,Q1 關閉,並且 VCC 透過 RC 施加到 Q2。基極電壓 –VBB1 和 –VBB2 以及門訊號的幅度進行調整,以便兩個電晶體電流相同,因此靜止輸出電壓電平將保持恆定。

如果門脈衝電壓與電晶體的 VBE 相比很大,那麼當每個電晶體不導通時,它都會被偏置到截止以下。因此,當門電壓出現時,Q2 將在 Q1 開始導通之前被驅動到截止狀態,而在門結束時,Q1 將在 Q2 開始導通之前被驅動到截止狀態。

下圖以更好的方式解釋了這一點。

因此,門訊號如上圖所示。門控訊號電壓將疊加在此波形上。如果門波形的上升時間與門持續時間相比很小,則這些尖峰將值可忽略不計。

該電路有一些缺點,例如

確定的上升和下降時間會導致尖銳的尖峰

透過 RC 的連續電流會散發出大量的熱量

兩個偏置電壓和兩個控制訊號源(彼此互補)使電路變得複雜。

除了這些缺點之外,該電路在降低閘電路中的基座方面很有用。