考慮8085微處理器的TOE時的最早資料輸出時間

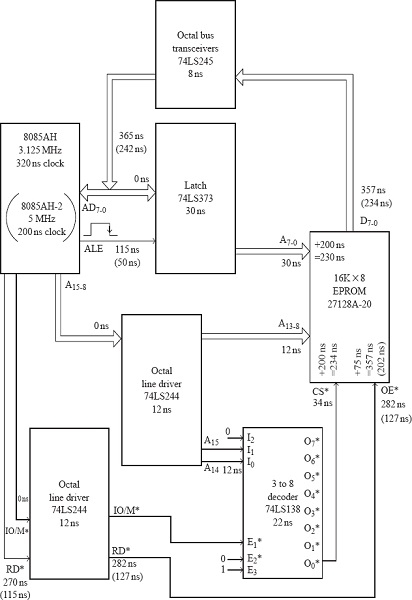

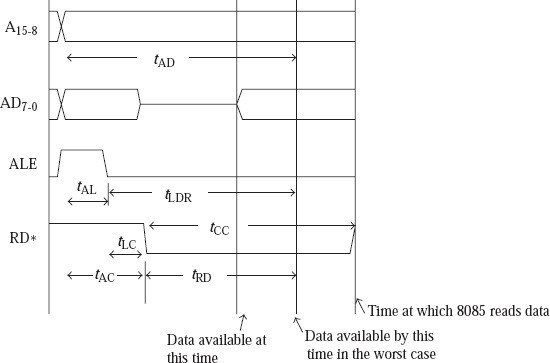

8085AH在270ns時啟用RD*訊號。該訊號透過八進位制線路驅動器74LS241延遲12ns後移動到27128的OE*引腳。因此,OE*訊號在282ns末尾被27128接收到。因此,資料只能在282ns+tOE=282ns+75ns+357ns內從小於27128的D7 到D0引腳輸出。

從之前的討論中可以清楚地看出,考慮到三個引數tACC、tCE和tOE,最早的資料輸出時間應為357ns。此外,tAcc可以是200ns+(357ns–230ns)等於327ns,而不會影響資料從儲存晶片輸出的時間。同樣,tCE可以大到200ns+(357ns–234ns),等於323ns,而不會影響資料從儲存晶片釋放的時間。

透過八進位制匯流排收發器74LS245以8ns的時延從27128接收資料。因此,8085AH在357ns+8ns等於365ns時接收到有效資料。

廣告

資料結構

資料結構 網路

網路 RDBMS

RDBMS 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP