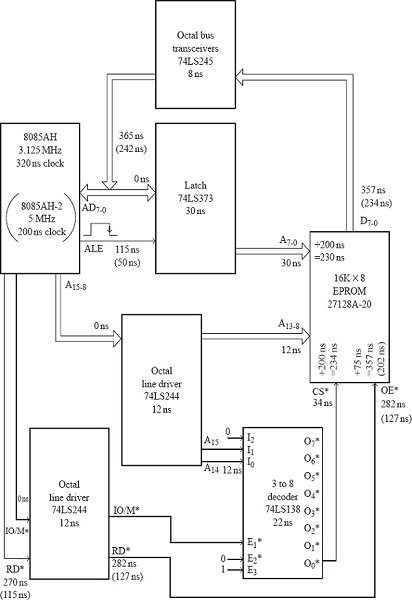

27128-20 與 8085 微處理器中 8085AH 的相容性檢查

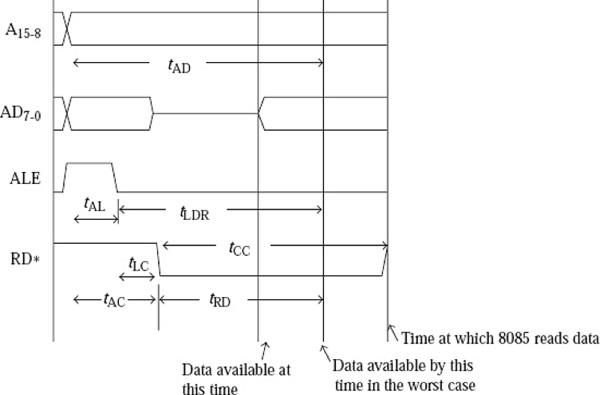

讓我們根據tAD、tLDR 和tRD 引數執行記憶體相容性檢查。

關於tAD的相容性:地址從 A15 到 A0 的有效地址與地址從 AD7 到 AD0 的有效資料之間的時間間隔。對於 8085AH,T 狀態工作時間為 320 nS,但最多可達 575 nS。但此處有效資料可用時間為 365 nS。因此,記憶體速度是相容的,並且有 575 nS - 365 nS = 210 nS 的額外時間裕度。

關於tLDR的相容性:算術邏輯單元尾隨邊沿與地址從 AD7 到 AD0 的有效資料之間的時間間隔,讀取操作。對於工作在 320 nS T 狀態的 8085AH,最大值為 460 nS。ALE 的尾隨邊沿出現在 115 nS。因此,在這種情況下,tLDR 僅為 365 nS - 115 nS = 250 nS。因此,記憶體速度是相容的,實際上有 460 nS - 250 nS = 210 nS 的額外時間裕度。

關於tRD的相容性:RD* 的前沿與地址相當於 AD7-0 的有效資料之間的時間間隔。對於工作在 320 nS T 狀態的,需要最大 300 nS。RD* 訊號由 8085 AH 在 270 nS 啟用,並由其在 365 nS 提供有效資料。

因此,27128-20 EPROM 晶片的速度與 8085AH 相容。因此,8085AH 與記憶體晶片介面,這些晶片具有如下所示的最壞情況規格

tAcc = 327 nS + 205 nS = 532 nS

tCE = 323 nS + 205 nS = 528 nS

tOE = 75 nS + 205 nS = 280 nS

在 ALS 套件中訪問 27128 EPROM 所涉及的延遲。

MR 機器週期匯流排時序特性

廣告

資料結構

資料結構 網路

網路 關係資料庫管理系統

關係資料庫管理系統 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 程式設計

C 程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP