什麼是二進位制加法器?

二進位制加法器是一種數位電路,它實現兩個長度支援任意二進位制數的算術和被稱為二進位制加法器。它使用按順序連線的全加器電路生成。輸出從一個全加器傳遞到下一個全加器的輸入傳輸。

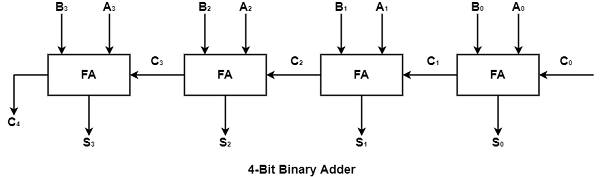

以下框圖演示了四個全加器電路的互連,以支援一個 4 位二進位制加法器。

A 被加數位元和 B 加數位元透過從右到左的下標數字建立,下標 0 表示低位位元。傳輸透過全加器以鏈方式連線。

二進位制加法器的輸入傳輸為 C0,輸出傳輸為 C4。全加器的 S 輸出建立所需的和位。

n 位二進位制加法器需要 n 個全加器。每個全加器的輸出進位連結到下一高位全加器的輸入進位。在 A 輸入部分的 n 位資料位來自包括 R1 在內的某個暫存器,在 B 輸入部分的 n 位資料位來自包括 R2 在內的另一個暫存器。求和可以傳輸到第三個暫存器或其中一個源暫存器(R1 或 R2),恢復其較早的內容。

廣告

資料結構

資料結構 網路

網路 關係型資料庫管理系統

關係型資料庫管理系統 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 語言

C 語言 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP