計算機體系結構中的載入/儲存重排序是什麼?

載入和儲存指令涉及影響處理器和記憶體的操作。在執行過程中,載入和儲存都必須首先等待其地址由算術邏輯單元 (ALU) 或地址單元計算。然後,載入可以訪問資料快取以獲取請求的記憶體資料,然後將其提供給暫存器。然後,載入通常透過將獲取的資料寫入指定的體系結構暫存器來完成。

儲存具有不同的執行模式。在接收到生成的地址後,儲存必須等待其運算元可用。與其他指令不同,儲存在運算元可用時即被認為已完成。現在讓我們考慮一下正在使用的 ROB。當 ROB 指示儲存在順序執行中接下來執行時,將要儲存的記憶體地址和資料被轉發到快取,並啟動快取儲存操作。

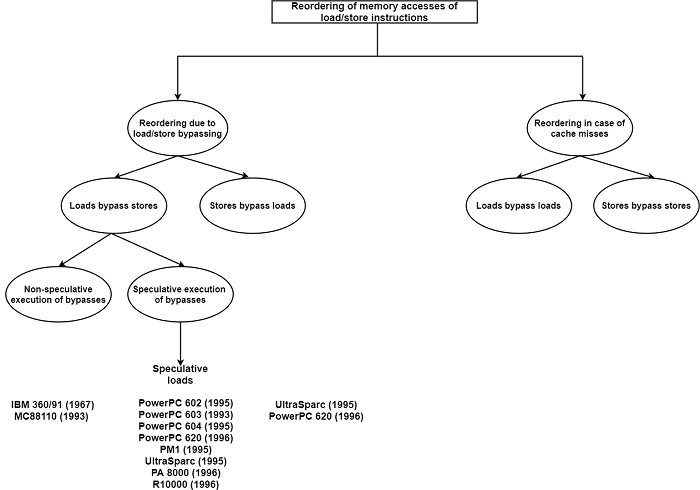

支援弱記憶體一致性的處理器允許記憶體訪問的重排序。這至少對三種方法有利:

- 它允許載入/儲存旁路。

- 它建立可實現的推測性載入或儲存

- 它使快取未命中保持隱秘

載入/儲存旁路意味著載入可以繞過掛起的儲存,反之亦然,前提是不違反記憶體資料依賴性。如圖所示,幾個最近的處理器允許載入繞過儲存,但反之則不行。

允許載入繞過儲存的優點是可以允許緊密迴圈的執行時重疊。透過允許迭代開始時的載入訪問記憶體而無需等待前一次迭代結束時的儲存完成,可以實現重疊。它可以避免獲取錯誤的資料值,只有當之前的儲存與載入的目標地址不相同時,載入才能繞過掛起的儲存。

對此情況更高階的處理是讓載入推測性地繞過儲存,也就是說,允許推測性載入。推測性載入避免將記憶體訪問延遲到所有必需的地址都已計算並且可以排除衝突的地址為止。

地址檢查通常透過將載入和儲存的計算目標地址寫入 ROB 或 DRIS 並在此處執行地址比較來執行。它可以降低所需電路的複雜性,地址檢查通常僅限於完整有效地址的一部分。

快取未命中是效能障礙的另一個來源,可以透過載入/儲存重排序來減少。快取未命中會導致所有後續相同型別的操作阻塞。

廣告

資料結構

資料結構 網路

網路 關係資料庫管理系統 (RDBMS)

關係資料庫管理系統 (RDBMS) 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 語言程式設計

C 語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP