計算機體系結構中的指令流水線是什麼?

指令流水線從記憶體中讀取連續的指令,而在其他段中,先前的指令正在執行。流水線處理出現在資料流和指令流中。這導致指令的獲取和執行重疊,從而執行同時操作。

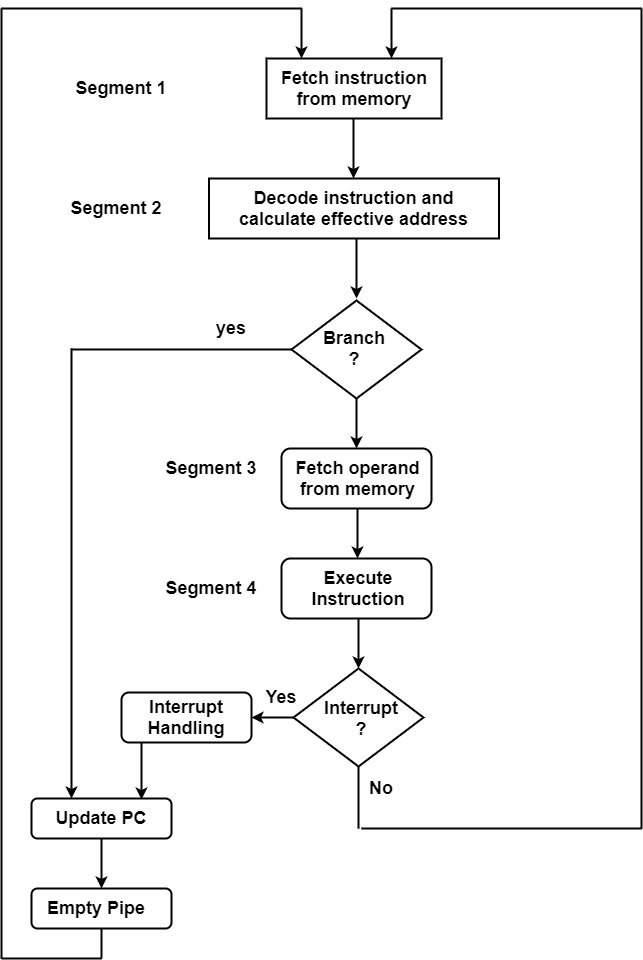

這種設計可能還與另一個事件相關,即指令可能會生成一個分支,跳出指令序列。在這種方法中,流水線被清空,並且分支指令之後從記憶體中讀取的所有指令都應被丟棄。

計算機可以構建為支援一個兩段單元,包括一個指令獲取單元和一個指令執行單元。使用先進先出 (FIFO) 緩衝區實現指令獲取段。

這是一種單元形成佇列而不是堆疊的方法。當執行單元未訪問記憶體時,控制器會遞增程式計數器並幫助其地址值從記憶體中讀取連續指令。

指令被插入到 FIFO 緩衝區中,以便執行以 FIFO 的方式出現。因此,指令流可以駐留在佇列中,等待執行段進行解碼和階段化。

因此,指令流排隊結構提供了一種有效的方法來減少讀取指令的記憶體平均訪問時間。只要 FIFO 緩衝區中有可用空間,控制單元就會啟動下一個指令獲取步驟。

緩衝區充當佇列,執行單元從中獲取指令以進行處理。

具有複雜指令的裝置除了獲取和執行之外,還需要其他步驟才能徹底處理指令。在這種方法中,裝置需要按照以下步驟序列處理每條指令。

- 它可以從記憶體中獲取指令。

- 它可以解碼指令。

- 它可以計算有效地址。

- 它可以從記憶體中獲取運算元。

- 它可以執行指令。

- 它可以將結果儲存到合適的位置。

多個段可能需要不同的時間來處理傳入的資料。這可能會阻止指令流水線以其最大速度執行。對於某些操作,會跳過一些段。

該圖顯示了指令流水線的示例。

段 1

可以使用先進先出 (FIFO) 緩衝區執行指令獲取段。

段 2

從記憶體中獲取的指令在第二個段中進行解碼。有效地址在一個獨立的算術電路中計算。

段 3

在第三個段中從記憶體中獲取運算元。

段 4

指令最終在流水線組織的最後一個段中執行。

廣告

資料結構

資料結構 網路

網路 關係資料庫管理系統

關係資料庫管理系統 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 程式設計

C 程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP