同步或時鐘控制的 SR 觸發器

在數位電子技術中,觸發器是許多電子電路中使用的最基本的儲存單元,用於儲存 1 位資訊。觸發器基本上是一個具有兩種穩定狀態的雙穩態多諧振盪器。

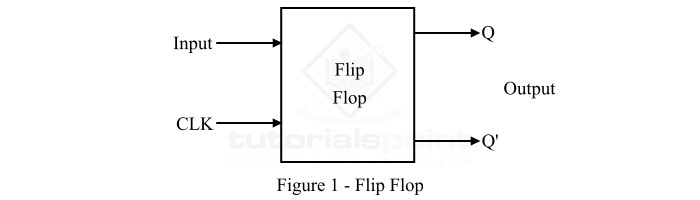

觸發器由邏輯閘的互連組成。然而,邏輯閘本身不具有儲存能力,但是當多個邏輯閘以特定方式排列時,它們可以儲存資訊。此外,觸發器是順序邏輯電路最基本的構建塊。典型觸發器的框圖如圖 1 所示。

觸發器具有一種或多種輸入和兩種輸出,通常用 Q 和 Q' 表示,以及一個時鐘輸入。時鐘輸入用於觸發觸發器,使其能夠改變其輸出的狀態。

有幾種型別的觸發器可用,例如 SR 觸發器、JK 觸發器、D 觸發器、T 觸發器。每種型別的觸發器都具有其獨特的特性和特性,適用於特定的應用。

同步觸發器和非同步觸發器

其邏輯電路由時鐘訊號時鐘/觸發器的觸發器被稱為同步觸發器。因此,即使其輸入多次變化,在沒有時鐘訊號的情況下,同步觸發器的輸出狀態也不會改變。

另一方面,非同步觸發器是沒有時鐘訊號的觸發器,因此其輸出在應用輸入時會立即改變。

現在,讓我們詳細討論時鐘控制或同步 SR 觸發器。

什麼是時鐘控制的 SR 觸發器?

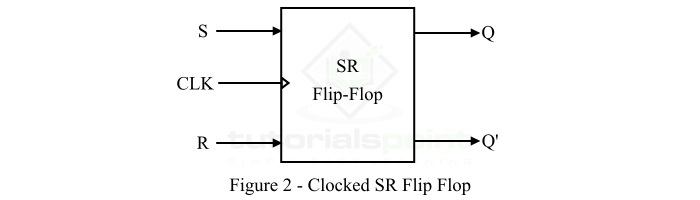

具有兩個輸入(即 S(置位)和 R(復位))的觸發器型別稱為SR 觸發器。如果觸發器的 S 和 R 輸入在存在時鐘脈衝時(即從低電平變為高電平或從高電平變為低電平)控制其輸出,則稱為時鐘控制的 SR 觸發器。由於時鐘訊號同步了 SR 觸發器的操作,因此時鐘控制的 SR 觸發器也稱為同步 SR 觸發器。時鐘控制或同步 S-R 觸發器的框圖如圖 2 所示。

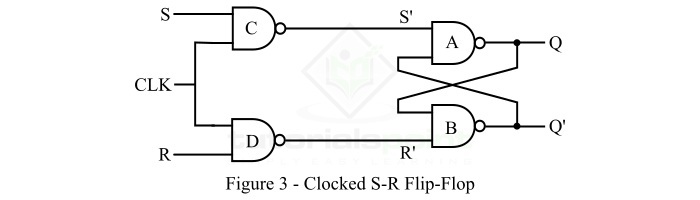

時鐘控制或同步 SR 觸發器的邏輯電路圖如下所示(圖 3)。

可以看出,該電路由四個 NAND 門組成。時鐘訊號連線到 NAND 門 C 和 D,輸入 S 和 R 也應用於 NAND 門 C 和 D。NAND 門 A 和 B 互連形成觸發器的儲存電路。

時鐘控制 SR 觸發器的操作

時鐘控制 SR 觸發器的電路操作如下所述:

當不施加時鐘訊號時,SR 觸發器電路保持非活動狀態,觸發器的輸出沒有變化。

當施加時鐘訊號時,觸發器電路變為活動狀態並按如下所述操作:

當 S = 0 且 R = 0 時,NAND 門 C 和 D 的輸出為 S' = 1 和 R' = 1。因此,NAND 門 A 和 B 的輸出保持不變。這稱為 SR 觸發器的保持狀態。

當 S = 0 且 R = 1 時,NAND 門 C 和 D 的輸出為 S' = 1 和 R' = 0,NAND 門 A 的輸出為 0,NAND 門 B 的輸出為 1。這稱為 SR 觸發器的復位狀態。

當 S = 1 且 R = 0 時,NAND 門 C 和 D 的輸出為 S' = 0 和 R' = 1,NAND 門 A 的輸出為 1,NAND 門 B 的輸出為 0。這稱為 SR 觸發器的置位狀態。

當 S = 1 且 R = 1 時,NAND 門 C 和 D 的輸出為 S' = 0 和 R' = 0,NAND 門 A 和 B 的輸出都試圖變為 1,這是不可能的。這稱為 SR 觸發器的禁止狀態。

我們也可以用真值表的形式表達時鐘控制 SR 觸發器的操作,如下所示。這裡,S 和 R 指定輸入,Qn 指定輸出的當前狀態,Qn+1 指定輸入變化和施加時鐘脈衝後輸出的狀態。

| 輸入 | 輸出 | 註釋 | ||

|---|---|---|---|---|

| S | R | Qn | Qn+1 | |

| 0 | 0 | 0 | 0 | 無變化/保持 |

| 0 | 0 | 1 | 1 | 無變化/保持 |

| 0 | 1 | 0 | 0 | 復位 |

| 0 | 1 | 1 | 0 | 復位 |

| 1 | 0 | 0 | 1 | 置位 |

| 1 | 0 | 1 | 1 | 置位 |

| 1 | 1 | 0 | X | 禁止 |

| 1 | 1 | 1 | X | 禁止 |

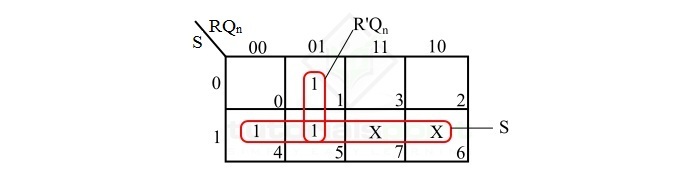

從時鐘控制 SR 觸發器的真值表中,我們可以直接寫出其輸出 Qn+1 的布林表示式如下:

因此,SR 觸發器的特性方程為:

$$Q_{n+1}=S+R'Q_{n}$$

時鐘控制 SR 觸發器的應用

時鐘控制 SR 觸發器用於以下應用:

數字計數器

儲存和移位暫存器

資料儲存單元

資料傳輸系統

分頻電路等。

結論

時鐘控制的 SR 觸發器是一種順序邏輯電路,用作數字系統中的 1 位儲存器件。它有兩個輸入 S(置位)和 R(復位)。當 R 為高電平時,SR 觸發器處於復位狀態;當 S 為高電平時,SR 觸發器處於置位狀態;當 S 和 R 輸入都為高電平時,SR 觸發器處於禁止或無效狀態;當 S 和 R 輸入都為低電平時,SR 觸發器處於無變化或保持狀態。

資料結構

資料結構 網路

網路 關係資料庫管理系統 (RDBMS)

關係資料庫管理系統 (RDBMS) 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 語言程式設計

C 語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP