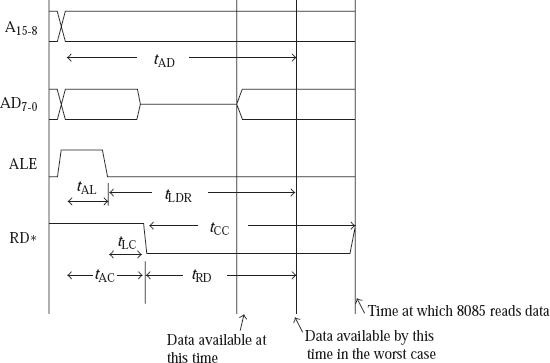

8085微處理器記憶體速度要求

在機器週期狀態T2結束時,8085處理器會檢測Ready輸入引腳。如果為邏輯0,則8085處理器進入Twait 狀態,否則進入T3狀態。Ready輸入永久固定為邏輯1。系統中的記憶體晶片和輸入/輸出埠與8085具有相同的速度。否則,外部電路應生成適當數量的等待狀態。實際上,在ALS套件中,Ready引腳應固定為邏輯1。

例如,我們檢查一下,如果使用27128A-20 16K×8 EPROM晶片,並且在不使用任何等待狀態的情況下與工作在320 nS時鐘週期的8085處理器一起使用。因此,對於介面記憶體晶片,最重要的時序引數是tcc、tCE和tOE。

對於27128A-20晶片,其特性如下。

tAcc最大值為200 nS

tCE最大值為200 nS

tOE最大值為75 nS

在以下假設下,在接收穩定地址後,資料輸出需要最多200 nS的時間。

記憶體晶片應至少在資料透過它輸出前200 nS (tCE)被選中。

在輸出資料之前,記憶體晶片的輸出使能線應至少啟用75 nS (tOE)。

廣告

資料結構

資料結構 網路

網路 RDBMS

RDBMS 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP