8085 微處理器中的記憶體對映 I/O

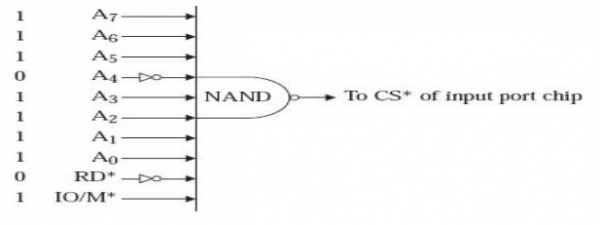

可以將 I/O 埠視為記憶體位置來定址。例如,假設當地址 = FFF0H、IO/M* = 0 和 RD* = 0 時,I/O 埠晶片的片選引腳被啟用。如下面的圖所示。

在這種情況下,當 8085 認為它正在為讀取操作定址記憶體位置 FFF0H 時,I/O 埠晶片被選中。請注意,8085 認為它正在定址記憶體位置,因為它已將 IO/M* 傳送為邏輯 0。但實際上,已選擇了輸入埠,並且輸入埠向 8085 提供資訊。這種被處理器視為記憶體位置定址的 I/O 埠稱為記憶體對映 I/O 埠。

在記憶體位置中,我們定址輸入輸出埠。例如,當地址 = FFF0H、IO/M* = 0 和 RD* = 0 時。在這裡,當 8085 微處理器發現它分配了記憶體位置時,我們選擇輸入輸出埠晶片,因為它像 IO/M* 一樣傳送邏輯 0。

但在現實世界中,我們選擇一個向 8085 微處理器提供資訊的輸入埠。像記憶體位置一樣,8085 微處理器被處理器定址,這些被稱為記憶體對映輸入輸出埠。

有一套用於此記憶體對映 I/O 操作的指令。例如 STA、LDA 等。讓我們詳細討論 STA 指令以更好地理解。

暫存器 A 是 8085 中用於執行算術、邏輯、I/O 和載入/儲存操作的 8 位暫存器。暫存器 A 通常稱為累加器。累加器是計算機 CPU(中央處理單元)中用於短期、中間儲存算術和邏輯資料的暫存器。在涉及兩個運算元的算術運算中,一個運算元必須位於此暫存器中。算術運算的結果將儲存或累積在此暫存器中。類似地,在涉及兩個運算元的邏輯運算中,一個運算元必須位於累加器中。此外,一些其他操作,如求補和十進位制調整,只能對累加器執行。

現在讓我們考慮一個僅涉及累加器內容的程式段。在 8085 指令集中,**STA** 是一個助記符,代表將累加器內容儲存到記憶體中。在此指令中,累加器 8 位內容將儲存到記憶體位置,其 16 位地址在指令中指示為 a16。此指令使用絕對定址來指定目標。此指令佔用 3 個位元組的記憶體。第一個位元組用於操作碼,接下來的兩個連續位元組提供 16 位地址,每個位元組連續分成 8 位。

| 助記符,運算元 | 操作碼(十六進位制) | 位元組 |

|---|---|---|

| STA 地址 | 32 | 3 |

讓我們以**STA 4050H**作為此類指令的示例。它是一個 3 位元組指令。第一個位元組將包含操作碼十六進位制值 32H。在 8085 組合語言編碼中,支援低位位元組的地址應首先提到,然後高位位元組的地址應接下來提到。因此,記憶體中的下一個位元組將儲存 50H,然後 40H 將儲存在最後一個第三個位元組中。假設累加器的初始內容為 ABH,記憶體位置 4050H 的初始內容為 CDH。因此,執行後,累加器內容將保持為 ABH,而 4050H 位置的內容將變為 ABH,替換其以前的內容 CDH。此指令的內容跟蹤顯示如下:

| 之前 | 之後 | |

|---|---|---|

| (A) | ABH | ABH |

| (4050H) | CDH | ABH |

此指令的內容跟蹤顯示如下

| 地址 | 十六進位制程式碼 | 助記符 | 註釋 |

|---|---|---|---|

| 2008 | 2A | STA 4050H | 記憶體位置 4050H 的內容 A |

| 2009 | 50 | 地址的低位位元組 | |

| 200A | 40 | 地址的高位位元組 |

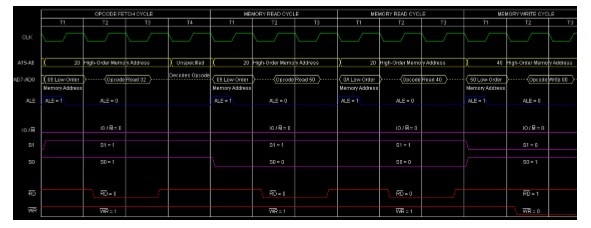

此指令**STA 4050H**的時序圖如下:

**總結** - 因此,此指令**STA 4050H**需要 3 個位元組、4 個機器週期(操作碼獲取、記憶體讀取、記憶體讀取、記憶體寫入)和 13 個 T 狀態才能執行,如時序圖所示。

資料結構

資料結構 網路

網路 RDBMS

RDBMS 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 程式設計

C 程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP