指令發出率的設計空間是什麼?

超標量處理器旨在為單個順序程式產生每時鐘週期超過一條指令的執行率。超標量處理器設計通常定義一組技術,使計算機的中央處理器 (CPU) 能夠在實現單個順序程式的同時獲得每週期超過一條指令的吞吐量。

超標量指令發出概念最早於 1970 年提出 (Tjaden 和 Flynn,1970)。後來在 20 世紀 80 年代得到了更精確的重新表述 (Torng,1982,Acosta 等人,1986)。

超標量處理器的功能是超標量指令發出。更高的發出率會導致更高的處理器效能,但同時也會放大控制和資料依賴性對處理器效能的限制性影響。

在超標量處理器中,每個週期發出多條指令,控制依賴性比標量處理器出現的頻率更高。頻率的增加大致與處理器的發出率成正比。

至於資料依賴性,更高的發出率也會嚴重阻礙處理器效能。在此考慮一下,例如在流水線處理器中,透過使用並行最佳化編譯器,大多數情況下可以避免由於依賴性造成的標量處理器發出阻塞。編譯器使用單獨的指令填充未使用的指令槽(稱為氣泡)。

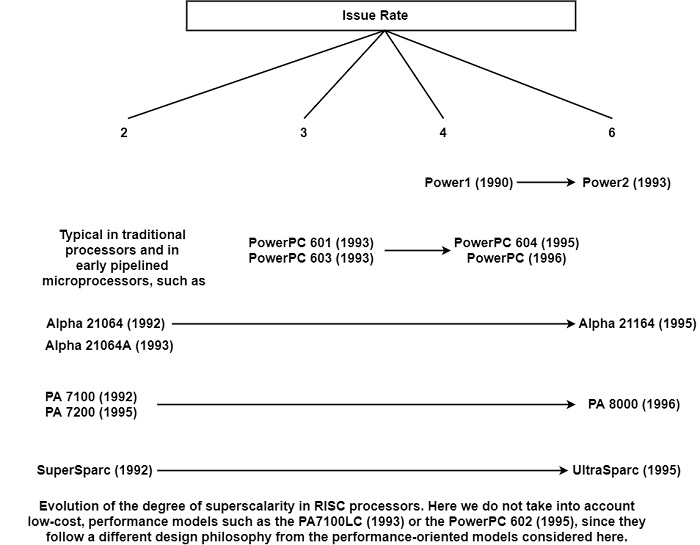

指令發出設計空間的第二個主要方面是發出率(超標量的程度)。此速率定義了超標量處理器在一個類似週期內可以發出的指令的最大數量。

超標量運算可以透過在每個週期發出兩條、三條或更多條指令來執行。更高的發出率提供了更高的效能,但是,它的執行更加困難。

超標量 CISC 處理器通常被控制為每個週期僅發出兩條或大約兩條指令。相比之下,早期的超標量 RISC 處理器每個週期經常發出兩條或三條指令。如所示,現代 RISC 處理器通常每個週期發出四條指令。

此圖顯示了五個特定 RISC 系列中發出率的演變。第一代 α 處理器 (α 21064 和 α 21064A) 和 HP 精確架構系列 (PA 7100、PA 7200) 的第一個超標量成員被控制為每個週期發出兩條指令。

相比之下,PowerPC 系列 (PowerPC 601、PowerPC 603) 和 SuperSparc 的第一個成員能夠每個週期發出三條指令,而 Power1 可以發出四條指令。

Power 2 在執行順序路徑時每個週期發出六條指令。但是,在猜測分支後,在開始執行目標路徑時,處理器僅發出四條指令。因此,Power2 現在是發出率的領導者。

資料結構

資料結構 網路

網路 關係資料庫管理系統 (RDBMS)

關係資料庫管理系統 (RDBMS) 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP