指令排程設計空間是什麼?

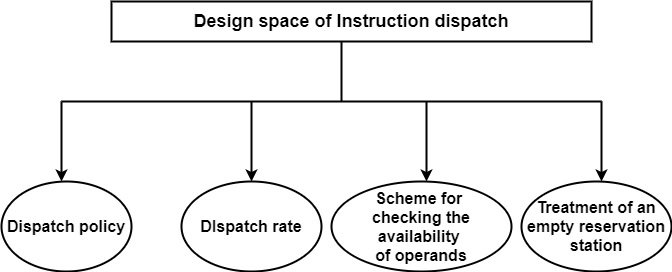

指令排程設計空間非常複雜。在某些方面,它類似於指令發出設計空間,但它還有兩個額外的方面,如圖所示。

排程策略 − 排程策略可以被認為是一個排程策略,包含以下元件:

選擇規則 − 選擇規則指定何時指令被認為可執行。我們假設使用了重新命名,並且未解決的條件轉移指令由推測性分支處理來管理。

仲裁規則 − 當多條指令符合執行條件,且下一週期只能排程一部分指令時,可能需要仲裁規則。大多數處理器使用簡單的仲裁規則,優先排程“較舊”的指令而不是“較新”的指令。Power1、Power2、PowerPC 620、PM1(Sparc64)和PentiumPro都是使用這種仲裁規則的例子。

排程順序 − 排程順序指定不可執行指令是否阻止所有後續指令被排程。

排程速率 − 設計空間需要額外的元件來確定每個保留站或DRIS每個週期可以排程多少條指令。這個元件稱為排程速率。

一個暫存緩衝區必須能夠在每個週期將一條指令排程到連線到它的任何EU(執行單元)。對於具有兩到三個EU的組站來說,這更容易實現,而對於連線了大量EU的中央站或DRIS來說則更難。例如,R10000使用組保留站。它的FX保留站每個週期可以排程兩條指令,每條指令排程到一個EU。

運算元可用性檢查方案 − 運算元的可用性需要在兩種情況下進行檢查:當運算元從暫存器檔案中獲取時,需要一個方案來檢查暫存器檔案中是否存在請求的內容。在指令排程期間,需要類似的方案來檢查暫存緩衝區中儲存的指令的所有運算元是否可用。它可以使用通常用於指示暫存器運算元可用性的技術,稱為記分板。

空保留站的處理 − 當指令到達空保留站時,超標量處理器遵循兩種不同的方法。直接的方法是以與部分填充的保留站相同的方式處理指令。但是,進入的指令必須在排程之前至少在一個空站中停留一個週期。Nx586是使用這種方法處理空保留站的處理器的例子。

處理空保留站的更高階方法是使用旁路。在這裡,一些額外的電路允許指令繞過空站,並立即轉發到EU,而無需任何額外的延遲。PowerPC 604和PM1(Sparc64)採用了這種更高效的方法。

資料結構

資料結構 網路

網路 關係資料庫管理系統 (RDBMS)

關係資料庫管理系統 (RDBMS) 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP