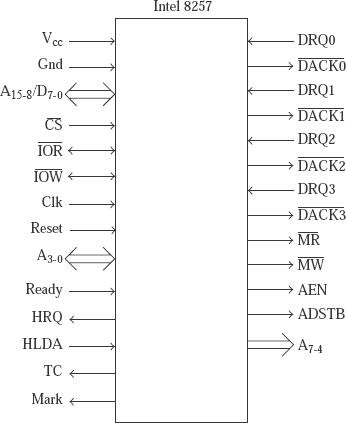

8257 引腳說明

下表描述了 8257 的引腳。

圖:英特爾 8257 的物理引腳圖

圖:英特爾 8257 的功能引腳圖

8257 使用 5V 電源。

| D7-0/A15-8 | 為了與處理器通訊,有 8 個雙向資料引腳,當處理器處於活動狀態且 8257 處於活動狀態時,它處於從模式。當處理器保持在 HOLD 狀態且 8257 充當主控時,它們用於傳送記憶體地址的最高 8 位。 | ||||||||||||||||||||||

| A3-0 | 當處理器處於活動狀態時,用作 8257 的地址輸入引腳。因此,為了選擇 8257 內部的暫存器之一,使用了這些引腳。

| ||||||||||||||||||||||

| 復位 | RESET 是一個高電平有效的輸入引腳,它連線到 8085 的 RESET OUT 引腳。8257 復位後,控制暫存器內容變為 00H。這意味著

| ||||||||||||||||||||||

| DRQ3-0 | 這些引腳是高電平有效的 DMA 請求輸入引腳,每個 DMA 通道分配一個。它們由一些特殊用途的 I/O 埠晶片啟用,例如 Intel 8257 軟盤控制器和 Intel 8275 CRT 控制器。在固定優先順序模式(當控制暫存器中的 RTPR 位為 0 時),DRQ0 具有最高優先順序,DRQ3 具有最低優先順序。 | ||||||||||||||||||||||

| DACK3-0* | 這些是低電平有效的 DMA 應答輸出引腳,每個四個 DMA 通道只有一個,英特爾 8275。 | ||||||||||||||||||||||

| IOR* | 當 8257 工作在從模式時,它是一個低電平有效的輸入引腳,由處理器啟用以讀取地址暫存器、計數器暫存器或狀態暫存器。 | ||||||||||||||||||||||

| IOW* | 當 8257 保持在從模式時,它是一個低電平有效的輸入引腳,由處理器啟用以寫入地址暫存器、計數器暫存器或控制暫存器。 | ||||||||||||||||||||||

| MR* | 當 8257 處於從模式時,它是一個低電平有效的輸出引腳,處於三態。當處理器保持在 HOLD 狀態時,8257 驅動該引腳。 | ||||||||||||||||||||||

| MW* | 它也是一個低電平有效的輸出引腳,當 8257 處於從模式時處於三態。當處理器處於 HOLD 狀態時,8257 驅動該引腳,該引腳在 DMA 寫機器週期時啟用,在 DMA 讀機器週期時變為非活動狀態。 | ||||||||||||||||||||||

| CS* | 與其他引腳不同,它也是一個低電平有效的輸入引腳,用於選擇晶片。 | ||||||||||||||||||||||

| Clk | 它是時鐘的輸入引腳。此時鐘的最大允許頻率約為 3 MHz。時鐘的輸入連線到基於 8085 的系統中 8085 的輸出。 | ||||||||||||||||||||||

| 就緒 | Ready 是一個高電平有效的輸入引腳,其功能類似於 8085 的 ready 輸入。具有慢訪問時間的裝置可以使用它在 DMA 讀取或寫入機器週期期間插入等待狀態。 | ||||||||||||||||||||||

| HRQ | HRQ 用於 HOLD 請求,它是一個高電平有效的輸出引腳,也連線到 8085 的 HOLD 輸入。每當 DRQ 輸入處於非活動狀態並且與其對應的 DMA 通道已啟用時,8257 都會啟用 HRQ 輸出,這實際上請求處理器授予系統匯流排的完全控制權。 | ||||||||||||||||||||||

| HLDA | HLDA 表示 HOLD 確認,它是一個高電平有效的輸入引腳,連線到 8085 的 HLDA 輸出。 | ||||||||||||||||||||||

| TC | TC 表示終端計數,它是一個高電平有效的輸出引腳。當正在服務的 DMA 通道的控制暫存器的所有 14 個最低有效位都變為 0 時,輸出變為啟用。 | ||||||||||||||||||||||

| MARK | 這也是一個高電平有效的輸出引腳,當正在服務的 DMA 通道的控制暫存器的最低有效 7 位變為 0 時啟用。換句話說,我們可以說每當控制暫存器的最低有效位元組變為 80H 或 00H 時。 | ||||||||||||||||||||||

| AEN | AEN 代表地址使能。它是一個高電平有效的輸出引腳。當 8085 成為計算機系統的匯流排主控時,Intel 8257 在 AEN 上輸出 0。 | ||||||||||||||||||||||

| ADSTB | ADSTB 表示地址選通,它是一個高電平有效的輸出引腳,執行與 8085 輸出相同的功能。在 Intel 8257 中,如果此引腳輸出為 0,則表示它處於從模式。 圖:顯示 8257 在基於 8085 的系統中介面的框圖 圖:顯示 8257 在基於 8085 的系統中介面的框圖 |

廣告

資料結構

資料結構 網路

網路 關係型資料庫管理系統

關係型資料庫管理系統 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 程式設計

C 程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP