低高電平輸出譯碼器

什麼是譯碼器?

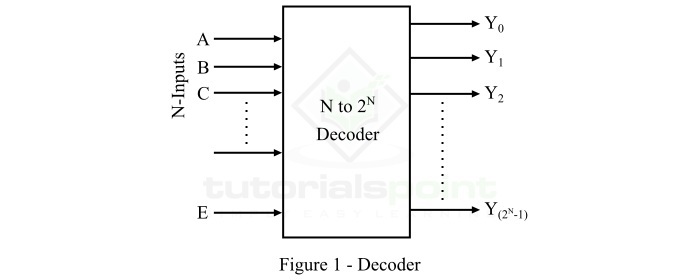

在數位電子學中,譯碼器是一種組合邏輯電路,它能夠將N個輸入的二進位制資訊轉換為最多2N個輸出。典型譯碼器的框圖如圖1所示。

可以看出,譯碼器有N條輸入線用於接收二進位制編碼資訊,一條使能輸入E用於開啟或關閉譯碼器(可選),以及2N條唯一的輸出線。

數字譯碼器廣泛應用於數位電子學領域的多種應用中,例如資料解碼、七段顯示器、資料多路複用和解複用、儲存器操作等。

低電平有效和高電平有效

在數字邏輯中,數字訊號有兩種狀態,即低電平有效和高電平有效。

在低電平有效狀態下,當數字訊號處於邏輯0電平或低電平狀態時,則認為其為高電平、有效或開啟。另一方面,當訊號處於邏輯1電平或高電平狀態時,則認為其為高電平、有效或開啟,這被稱為訊號的高電平有效狀態。

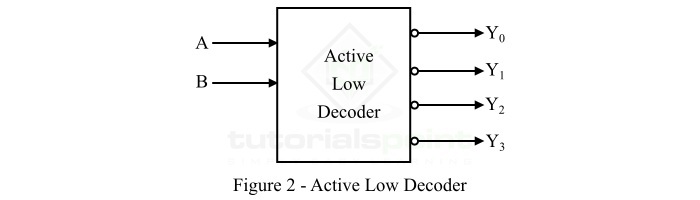

現在,讓我們瞭解一下低電平和高電平輸出譯碼器的操作。為此,我們考慮一個2到4線的譯碼器,它有兩個輸入(假設為A和B)和四個輸出,即Y0、Y1、Y2和Y3。因此,讓我們從低電平輸出譯碼器開始。

什麼是低電平有效譯碼器?

根據輸入組合將二進位制輸入程式碼轉換為特定輸出程式碼/訊號的譯碼器型別,其中當譯碼器的輸出處於邏輯0狀態時,則認為其為有效或開啟,稱為低電平有效譯碼器。2到4線低電平有效譯碼器的框圖如圖2所示。

低電平有效2到4線譯碼器的真值表如下所示:

| 輸入 | 輸出 | ||||

|---|---|---|---|---|---|

| A | B | Y0 | Y1 | Y2 | Y3 |

| 0 | 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 0 |

從真值表中,我們可以看到

當輸入A和B都為低電平時,輸出Y0有效(低)。

當輸入A為低電平且B為高電平時,輸出Y1有效(低)。

當輸入A為高電平且B為低電平時,輸出Y2有效(低)。

當輸入A和B都為高電平時,輸出Y3有效(低)。

從真值表中,我們可以看到當譯碼器的輸出處於低電平狀態,即邏輯0狀態時,則認為其有效。因此,它被稱為低電平有效譯碼器。我們可以直接寫出低電平有效譯碼器每個輸出的表示式,如下所示:

$$Y_{0}\, =\left ( A+B \right )$$

$$Y_{1}\, =\left ( A+\bar{B} \right )$$

$$Y_{2}\, =\left ( \bar{A}+B \right )$$

$$Y_{3}\, =\left ( \bar{A}+\bar{B} \right )$$

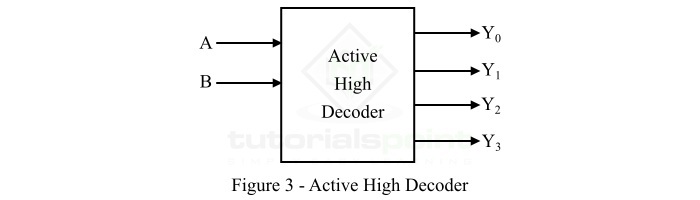

現在,讓我們討論一下高電平有效譯碼器。

什麼是高電平有效譯碼器?

根據輸入組合將二進位制輸入程式碼轉換為特定輸出程式碼/訊號的譯碼器型別,其中當譯碼器的輸出處於邏輯1狀態時,則認為其為有效或開啟,稱為高電平有效譯碼器。2到4線高電平有效譯碼器的框圖如圖3所示。

2到4線高電平有效譯碼器的真值表如下所示:

| 輸入 | 輸出 | ||||

|---|---|---|---|---|---|

| A | B | Y0 | Y1 | Y2 | Y3 |

| 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

從真值表中,我們可以看到

當輸入A和B都為低電平時,輸出Y0有效(高)。

當輸入A為低電平且B為高電平時,輸出Y1有效(高)。

當輸入A為高電平且B為低電平時,輸出Y2有效(高)。

當輸入A和B都為高電平時,輸出Y3有效(高)。

從真值表中,我們可以看到當譯碼器的輸出處於高電平狀態或邏輯1狀態時,則認為其有效。因此,它被稱為高電平有效譯碼器。我們可以直接寫出高電平有效譯碼器每個輸出的表示式,如下所示:

$$Y_{0}=\bar{A}\bar{B}$$

$$Y_{1}=\bar{A}B$$

$$Y_{2}=A\bar{B}$$

$$Y_{3}=AB$$

這就是關於低電平輸出和高電平輸出譯碼器的所有內容。

資料結構

資料結構 網路

網路 RDBMS

RDBMS 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP