什麼是VLIW架構?

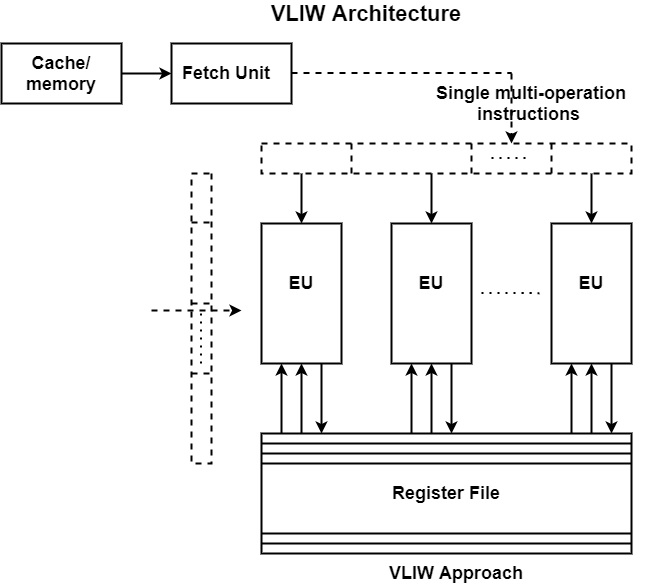

VLIW代表超長指令字。它是一種指令集架構,旨在充分利用指令級並行性 (ILP) 進行改進的實現。中央處理器允許程式僅按順序確定要執行的指令,而VLIW處理器允許程式顯式定義要並行執行的指令。這種設計旨在實現更高的效能,而不會像某些多指令設計那樣複雜。

VLIW方法需要超長指令字來定義每個執行單元必須執行的操作。如果假定有n個執行單元,則VLIW指令的長度是傳統RISC指令字長度的n倍。因此,包含大約十個執行單元的VLIW處理器需要數百位的字長。例如,Trace VLIW系列可以並行執行7到28條指令(取決於包含的模組數量(1-4)),字長為256-1024位。

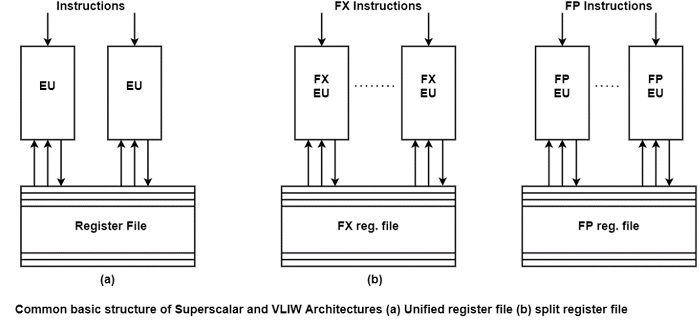

VLIW架構與超標量處理器密切相關。兩者都旨在透過處理指令級並行性來加快計算速度。兩者具有相似的執行機制,它主要包括多個並行執行的執行單元(EU),並使用統一暫存器檔案來處理所有資料型別,或者像圖中所示的那樣,為FX和FP資料使用不同的(分離的)暫存器檔案。

VLIW和超標量處理器的區別在於指令的生成方式和排程方式。超標量架構旨在獲取為順序處理器設計的常規指令。VLIW架構包含長指令字,其中包括每個可用執行單元的控制欄位(對於統一暫存器檔案設計)。

VLIW架構是靜態排程的。靜態排程消除了處理器指令排程的負擔,並將此功能完全委託給編譯器。靜態排程對於VLIW架構非常有利,因為它大大降低了複雜性。

與類似的超標量設計相比,VLIW設計的優勢在於其較低的複雜性,從而可以實現更高的時鐘頻率。在靜態排程中,編譯器完全負責檢測和消除控制、資料和資源依賴性。

明顯的代價是編譯器的複雜性,但還存在更不利的後果。為了能夠排程操作,必須向編譯器提供相當詳細的VLIW架構設計。這意味著編譯器必須熟悉處理器的所有重要特性和記憶體,包括可用執行單元的數量和型別、它們的延遲和重複成本、記憶體載入使用延遲等。

資料結構

資料結構 網路

網路 關係資料庫管理系統 (RDBMS)

關係資料庫管理系統 (RDBMS) 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP