什麼是 VLIW 架構?

VLIW 代表超長指令字 (VLIW) 架構。它是利用程式中指令級並行 (ILP) 的一種合適替代方案,尤其是在一次執行多個基本(原始)指令時。

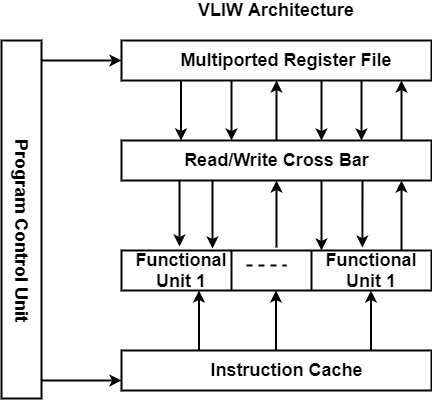

這些處理器包括各種功能單元,從指令快取中獲取包含各種原始指令的超長指令字,並排程整個 VLIW 以進行並行執行。

這些功能由編譯器利用,編譯器生成已將可並行執行的單獨原始指令分組的程式碼。處理器具有關聯簡單的控制邏輯,因為它們不實現任何動態排程或操作重新排序。

VLIW 的主要目標是消除大多數現代微處理器中出現的複雜的指令排程和並行排程。VLIW 處理器應該比可比的 RISC 晶片更快且成本更低。

如圖所示,多個功能單元共享一個通用的多埠暫存器檔案以獲取運算元並存儲結果。功能單元對暫存器檔案的並行隨機訪問由讀/寫交叉開關實現。功能單元中操作的執行與資料在 RAM 和暫存器檔案之間進行載入/儲存操作同時進行。

VLIW 架構的優點

- 它可以提高效能。

- 它用於潛在的可擴充套件性。

- 可以插入更多實現單元,因此更多指令可以溢位到 VLIW 指令中。

VLIW 架構的缺點

- 它可以被新程式設計師使用。

- 程式應跟蹤指令排程。

- 它會導致記憶體使用增加。

- 它用於高功耗。

廣告

資料結構

資料結構 網路

網路 關係資料庫管理系統

關係資料庫管理系統 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 程式設計

C 程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP