計算機體系結構中的內部晶片組織是什麼?

內部組織是線性的。該晶片具有三個地址輸入和兩個資料輸出,以及 16 位內部儲存器,構造為八個 2 位位置。三個地址位被解碼以選擇八個位置中的一個,但僅當晶片使能有效時才如此。如果 CE = 0,則解碼器被停用,並且不選擇任何位置。

該位置單元的三態緩衝器被使能,允許資料移動到輸出緩衝器。如果 CE 和 OE 都設定為 1,則這些緩衝器被使能,並且資料從晶片輸出,因此,輸出處於三態。

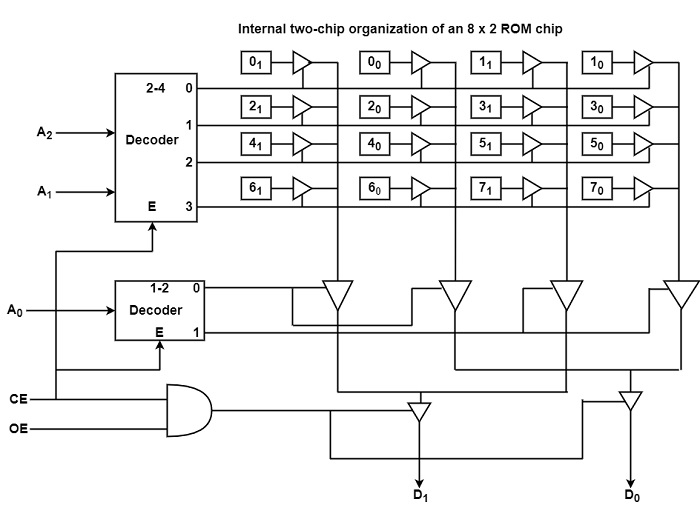

隨著多個位置的改進,線性組織中所需的解碼器地址的大小變得過高。可以使用多維解碼來發明記憶體晶片。為了說明這種組織,請考慮圖中所示的相同 8 x 2 ROM 晶片的二維組織。

此配置具有四行,每行四位,每行儲存兩個資料值。例如,ROM 的第一行包含地址 0 和 1 處的資料。每行中兩個位置的兩個高階地址位相同。

這兩個高階地址位是從四行中的一行選擇的,低階地址位選擇行中的兩個位置之一。

在較大的記憶體晶片中,這種節省可能很重要。考慮一個 4096 x 1 晶片。線性組織將需要一個 12 到 4096 的解碼器,其大小與多個輸出成比例。

n 到 2n 解碼器的大小據說為 O(2n)。如果晶片改為構建為 64 x 64 的二維陣列,則它將有兩個 6 到 64 的解碼器:一個用於選擇 64 行之一,另一個用於選擇行內的 64 個單元之一。解碼器的大小與 2 x 64 成比例,或 O(2 x 2n/2) = O($2^{\frac{n}{2}+1}$)。

廣告

資料結構

資料結構 網路

網路 關係資料庫管理系統 (RDBMS)

關係資料庫管理系統 (RDBMS) 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP