微指令序列器的實現

概述

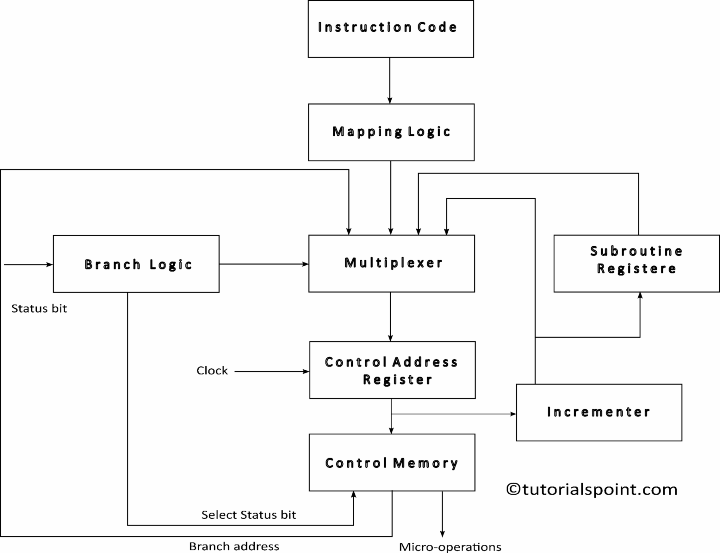

數字處理器過程可以透過微程式控制單元靈活地管理。微指令序列器是負責檢索和執行微指令的關鍵元件,位於微程式控制單元的核心。本文將探討微指令序列器的設計,並瞭解其如何實現。

微指令序列器

在採用微程式的計算機中,管理微指令序列的電路稱為微指令序列器。它負責生成下一條要執行的微指令的地址,並確保它們按正確的順序執行。

微指令序列器通常包含以下元件:

儲存微指令的控制儲存器。

程式計數器 (PC),儲存當前微指令的地址。

一個控制器,生成下一條要執行的微指令的地址。

一個定時電路,確保微指令按正確的順序執行。

微指令按順序儲存在控制儲存器中。序列中第一條微指令的地址作為 PC 的初始化點。序列控制器生成下一條要執行的微指令的地址。定時電路確保微指令按正確的順序執行。

實現

將微指令序列器投入使用的過程涉及建立微程式控制單元獲取和執行微指令所需的部件和邏輯。以下是實現過程的總體描述:

設計控制儲存器

確定實現適當的控制訊號集所需的微指令數量。

在設計控制儲存器時,使用合適的儲存器技術,例如 ROM 或 PLA(可程式設計邏輯陣列)。

分配每個微指令的地址和相關的控制訊號。

計算機程式計數器

建立一個程式計數器,跟蹤下一條要獲取的微指令的位置。

根據控制儲存器中微指令的數量計算程式計數器的寬度。

獲取微指令

使用程式計數器訪問控制儲存器並獲取位於指定地址的微指令。

獲取的微指令通常被放置在微指令暫存器 (MIR) 中,用於解碼和生成控制訊號。

生成控制訊號

解碼獲取的微指令以獲得各種 CPU 元件所需的控制訊號。

根據解碼的微指令建立邏輯電路或控制訊號生成器以生成所需的控制訊號。

組合邏輯電路、多路複用器或其他合適的部件可用於生成控制訊號。

邏輯排序

建立排序邏輯以管理微指令的流程。

根據微程式的複雜性,可以使用基於計數器的技術或有限狀態機 (FSM) 來實現此邏輯。

在程式中新增控制流指令,例如條件分支和跳轉,以根據特定條件更改微指令的順序。

計算下一個地址

確定將用於確定下一條要獲取的微指令地址的邏輯。

程式計數器可能需要遞增以獲取下一條順序的微指令,或者根據分支和跳轉等控制流指令進行修改。

執行監督

建立確保微指令正確執行所需的定時和控制電路。

協調微指令的定時和排序,以確保控制訊號在正確的時間和持續時間內生成。

重複這些步驟以獲取每條微指令

對儲存在控制儲存器中的每條微指令重複步驟 3 到 7,確保以正確的順序生成和執行所有必需的控制訊號。

結論

微指令序列器的開發是微程式控制單元的一個關鍵組成部分。它透過檢索、解碼和生成必要的控制訊號,簡化了微指令的有效執行。透過仔細設計控制儲存器、程式計數器、排序邏輯和控制訊號生成,設計人員可以構建一個強大的微指令序列器,有效地控制微程式處理器的操作。微指令序列器對於實現控制靈活性至關重要,使處理器能夠有效地執行各種操作並執行復雜指令。

資料結構

資料結構 網路

網路 RDBMS

RDBMS 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C 程式設計

C 程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP