8212 非可程式設計8位I/O埠

輸入輸出埠分為兩種:可程式設計輸入輸出埠和非可程式設計輸入輸出埠。由於可程式設計輸入輸出埠的功能可以透過軟體改變,因此它們變得更受歡迎。我們不需要改變線路,而是改變I/O埠的硬體來改變其功能。Intel 8255是一個基於埠的流行輸入輸出晶片。而對於非可程式設計I/O埠,需要改變線路或硬體來改變其完整功能。我們稍後會看到,當8212作為輸入埠而不是輸出埠工作時,需要改變連線。這些非可程式設計的輸入輸出埠設計簡單。

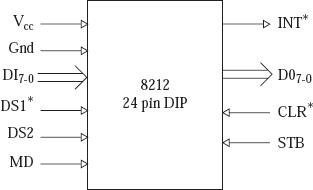

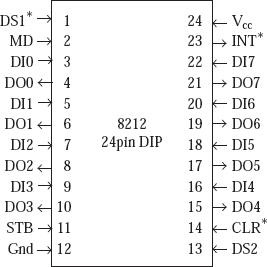

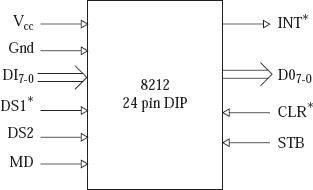

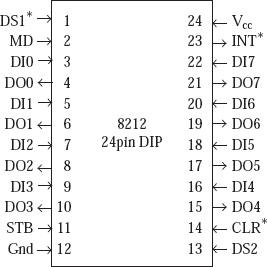

如今,我們發現8212作為雙列直插式封裝晶片,共有24個引腳。

它需要+5V的直流電源才能工作。8212中的8位鎖存器接收來自DI7到DI0的八個資料輸入上的資訊。幫助資訊鎖存的條件取決於MD引腳的邏輯狀態。鎖存器中的資訊透過D7-D0資料輸出引腳輸出。資訊鎖存的條件取決於MD引腳。

如今,我們發現8212作為雙列直插式封裝晶片,共有24個引腳。

它需要+5V的直流電源才能工作。8212中的8位鎖存器接收來自DI7到DI0的八個資料輸入上的資訊。幫助資訊鎖存的條件取決於MD引腳的邏輯狀態。鎖存器中的資訊透過D7-D0資料輸出引腳輸出。資訊鎖存的條件取決於MD引腳。

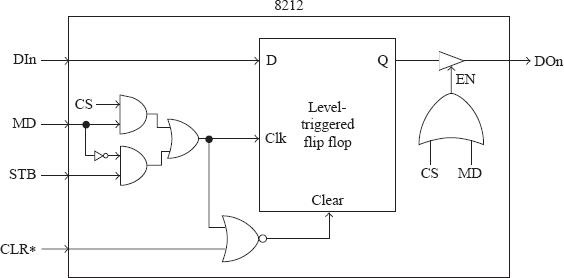

8212依賴於邊沿觸發的D型觸發器。我們稱之為服務請求觸發器。它負責在INT*引腳上生成中斷請求。INT*是一個低電平有效的輸出引腳,在中斷驅動的資料傳輸方案中很有用。負責啟用INT*訊號的內部架構如下所示

當DS1*為0且DS2為1時,內部晶片選擇訊號被啟用。

當STB由高電平轉為低電平時,內部訊號SQ為0。

圖:8212中觸發器鎖存的連線細節

從圖中可以得出以下結論:當MD為1時,CS充當鎖存器的時鐘;當MD為0時,STB充當鎖存器的時鐘。當時鍾處於高電平時,鎖存器的輸出Q跟隨相應的DI輸入。當時鍾由高電平轉為低電平時,資料鎖存開始起作用。當EN訊號被啟用時,輸出Q處的資料透過相應的DO引腳輸出。當CS等於1或MD等於1時,EN訊號被啟用。

簡要概述一下引腳:

| Vcc | 始終連線到+5V的直流電源。 |

| Gnd | 連線到地。 |

| MD | 模式輸入引腳,確定鎖存器的時鐘源。如果MD為0,則STB充當鎖存器的時鐘輸入;如果MD為1,則CS充當時鐘輸入。 |

| STB | 脈衝輸入。 |

| DS1*, DS2 | 器件選擇引腳。 |

| DI7-0 | 八個資料輸入,從D7到D0。 |

| DO7-0 | 資料輸出。 |

| INT* | 中斷輸出引腳,用於中斷微處理器。 |

| CLR* | 非同步清零輸入,低電平有效。 |

資料結構

資料結構 網路

網路 關係資料庫管理系統 (RDBMS)

關係資料庫管理系統 (RDBMS) 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C語言程式設計

C語言程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP