計算機體系結構中的暫存器和記憶體控制是什麼?

暫存器和記憶體的控制輸入為:

- 載入 (LD) − 啟用時,可以將內容從源暫存器或記憶體傳輸到/從匯流排傳輸。

- 增量 (INR) − 它可以將暫存器加1。

- 清零 (CLR) − 它可以清零暫存器。

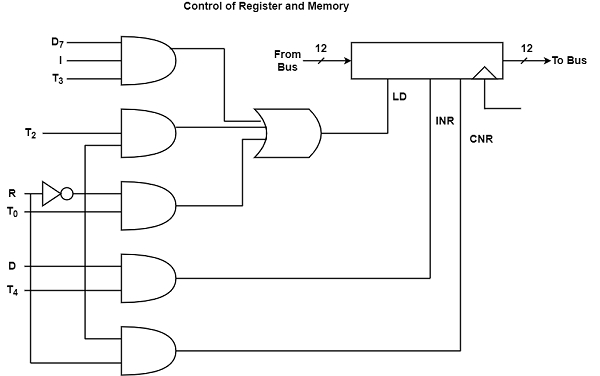

該圖顯示了暫存器和記憶體控制方案。

如框圖所示,所有暫存器傳輸語句最初都會被檢查,這會修改AR的內容。

指令如下:

| R′T0 | AR ← PC |

| R′T2 | AR ← IR(0 − 11) |

| D′7IT3 | AR ← M[AR] |

| RT0 | AR ← 0 |

| D5T4 | AR ← AR + 1 |

前三個語句確定資料從暫存器或記憶體到AR的傳輸。源暫存器或記憶體的內容位於總線上,透過啟用其LD控制輸入將匯流排內容傳輸到AR。第四個語句將AR清零。最後一個語句將AR加1。

控制功能可以組合成三個布林表示式,如下所示:

| LD(AR) | R′T0 + R′T2 + D′7 IT3 |

| CLR(AR) | RT0 |

| INR(AR) | D5T4 |

其中LD(AR)是AR的載入輸入,CLR(AR)是AR的清零輸入,INR(AR)是AR的增量輸入。與AR相關的控制門邏輯顯示在圖中。

同樣,我們可以更改其他暫存器的控制門,以及控制記憶體讀寫輸入所需的邏輯。透過檢查表以查詢確定讀取操作的語句來更改與記憶體讀取輸入相關的邏輯閘。讀取操作從符號←M [AR] 中識別。

讀取 = R′T1 + D′7 IT3 + (D0 + D1 + D2 + D6 )T4

執行布林表示式的邏輯閘的輸出應連線到記憶體的讀取輸入。

廣告

資料結構

資料結構 網路

網路 關係資料庫管理系統 (RDBMS)

關係資料庫管理系統 (RDBMS) 作業系統

作業系統 Java

Java iOS

iOS HTML

HTML CSS

CSS Android

Android Python

Python C程式設計

C程式設計 C++

C++ C#

C# MongoDB

MongoDB MySQL

MySQL Javascript

Javascript PHP

PHP